**TM 11-5815-365-14-4-1 NAVELEX 0967-426-2010** TO 31W4-2FG-1351-4-1

#### BULLETIN 302B VOL 1 OF 3

#### TECHNICAL MANUAL MASTER AND SUPPLEMENTARY HIGH SPEED TAPE SENDER, AND HIGH SPEED TAPE RECEIVER FOR THE MULTIPLE ADDRESS PROCESSING SYSTEM (MAPS)

(A MODEL)

This publication *replaces* all previously dated Army and Navy manuals, and the Air Force TO 31W4-2FG-1351 Vol 4 of 6 In part.

MARCH 1972

TM-11-5815-365-14-4-1 NAVELEX 0967-426-2010 TO 31W4-2FG-1351-4-1

REPRINTED BY COURTESY OF THE TELETYPE CORPORATION. (Reprinted by FMC-98230, MARCH 1972)

BULLETIN 302B VOL 1 OF 3

TECHNICAL MANUAL MASTER AND SUPPLEMENTARY HIGH SPEED TAPE SENDER, AND HIGH SPEED TAPE RECEIVER FOR THE MULTIPLE ADDRESS PROCESSING SYSTEM (MAPS)

(A MODEL)

This publication replaces all previously dated Army and Navy manuals, and the Air Force TO 31W4-2FG-1351 Vol 4 of 6 in part.

READER PLEASE NOTE: As of 8 September 1971, this BULLETIN consists of five volumes.

MARCH 1972

#### **302B** VOLUME 1

#### INTRODUCTION

Bulletin 302B is a technical manual for the Master and Supplementary High Speed Tape Sender, and High Seed Tape Receiver used in the Multiple Address Processing System (MAPS).

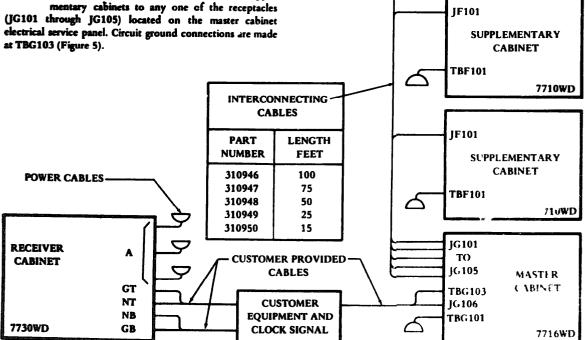

This bulletin now consists of three volumes. Volume 1 contains the Master, Supplementary, and Receiver sections, which provide description and theory of operation, installation, troubleshooting, adjustments, removal and replacement of components, and lubrication. Volume 1 must be used in conjunction with Bulletins 279B Technical Manual High Speed Tape Punch (DRPE), and 301B High Speed Tape Reader (DX Type).

Volume 2 contains the master sender wiring diagrams, (actuals, circuit cards, and schematics). Volume 3 contains the supplementary sender, and receiver cabinet wiring diagrams, (actuals, circuit cards, and schematics).

Eachvolume is made up of a group of individual sections. The sections are separately identified by title and section number, and the pages are numbered consecutively, independent of other sections. The identifying nine-digit number appears on each page of the section in the upper right-hand corner of right-hand pages, and in the upper leftcomer of left-hand pages.

To locate specific information, refer to the table of contents on the following page. Look for the name of the equipment involved in the heft-handcolumn, the associated section title is found in the next column, and the identifying section number is found in the righthand column.

The sections are arranged in the bulletin, in the order shown in the table of contents. Turn to page one of the indicated section where the table of contents will be found (except where a section is small and does not require a listing of contents).

NOTE: For parts ordering information refer to Bulletin 1208B.

#### TABLE OF CONTENTS

| <u>Equipment</u>                                                                                               | Contents                                                              | Section       | Issue |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|-------|

| Master and Supplementary High Speed<br>Tape Sender for the Multiple Address<br>Processing System (MAPS)        | Description, and Theory of Operation                                  | 592-851-130TC | 2*    |

| Master and Supplementary High Speed<br><b>Tape Sender for the</b> Multiple Address<br>Processing System (MAPS) | Installation                                                          | 592-851-230TC | 2*    |

| Master and Supplementary High Speed<br>Tape Sender for the Multiple Address<br>Processing System (MAPS)        | Troubleshooting                                                       | 592-851-330TC | 2*    |

| Master and Supplementary High Speed<br>Tape Sender for t&e Multiple Address<br>Processing System (MAPS)        | Adjustments, <b>and Removal</b><br>and Replacement of Com-<br>ponents | 592-851-730TC | 2*    |

| Master and Supplementary High Speed<br>Tape Sender for the Multiple Address<br>Processing System (MAPS)        | Lubrication                                                           | 592-851-731TC | 2**   |

| High Speed Tape Receiver for the Multi-<br>ple Address Processing System (MAPS)                                | Description, and Theory of Operation                                  | 592-852-130TC | 2*    |

| High Speed Tape Receiver for the Multi-<br>ple Address Processing System (MAPS)                                | Illustration                                                          | 592-852-230TC | 2*    |

| High Speed Tape Receiver for the Multi-<br>ple Address Processing System (MAPS)                                | Troubleshooting                                                       | 592-852-330TC | 2*    |

| High Speed Tape Receiver for the Multi-<br>Address Processing System (MAPS)                                    | Adjustments, and Removal<br>and Replacement of Com-<br>ponents        | 592-852-730TC | 2*    |

| High Speed Tape Receiver for the Multi-<br>ple Address Processing System (MAPS)                                | Lubrication                                                           | 592-852-731TC | 2**   |

\*Indicates changes. \*\*Indicates a new section added to this bulletin.

<u>Note 1</u>: This bulletin now consists of three volumes. Sections originally in Bulletin 302B have been revised. New sections have been added in each volume.

<u>Note 2</u>: Circuit Description information formerly in Section 592-851-430TC is now contained in Section 592-851-130TC. Section 592-951-420TC contains schematic drawings and will be found in Volume 2. Lubrication information formerly in Section 592-851-730TC can be found in Section 592-851-731TC.

<u>Note 3</u>: Circuit Description information formerly in Section 592-852-430TC is now contain in Section 592-852-130TC. Section 592-852-430TC contains schematic drawings and will be found in Volume 2. Lubrication information formerly in Section 592-852-790TC can be found in Section 592-852-791TC.

### MASTER AND SUPPLEMENTARY HIGH SPEED TAPE SENDER FOR THE MULTIPLE ADDRESS PROCESSING SYSTEM (MAPS) DESCRIPTION AND THEORY OF OPERATION

| CONTENTS                                                                                                                                                                                                    | PAGE                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1. GENERAL                                                                                                                                                                                                  | <br>. 1                       |

| 2. DESCRIPTION                                                                                                                                                                                              | <br>. 1                       |

| ASSOCIATED EQUIPMENT                                                                                                                                                                                        | <br>. 4                       |

| TECHNICAL DATA                                                                                                                                                                                              | <br>. 4                       |

| A. Temperature and Power         Specifications         B. Input Signal Requirements         C. Input Signal Characteristics         D. Output Signal Requirements         E. Output Signal Characteristics | <br><br><br>. 4<br>. 4<br>. 4 |

| MASTER TAPE SENDER LOGIC                                                                                                                                                                                    | <br>. 5                       |

| A.ModulesB.Modules A and EC.Module BD.Alarms                                                                                                                                                                | <br><br>. 6<br>. 6            |

| TAPE TRANSPORT MECHANISM                                                                                                                                                                                    | <br>6                         |

| TAPE THREADING                                                                                                                                                                                              | 6                             |

| 3. THEORY OF OPERATION                                                                                                                                                                                      |                               |

| CIRCUIT DESCRIPTION                                                                                                                                                                                         | <br>. 9                       |

| SUPPLEMENTARY READER LOGIC                                                                                                                                                                                  | <br>. 11                      |

| A. Bid Circuitry                                                                                                                                                                                            | <br>. 11                      |

| Circuitry                                                                                                                                                                                                   | <br>. 14                      |

~ ~ . . . . . . . . . . . . . .

| CONTENTS P               | AGE      |

|--------------------------|----------|

| MASTER TRANSMITTER LOGIC | 15       |

| A. Reader Logic          | 20<br>24 |

#### 1. GENERAL

1.01 This section provides description and theory of operation for the master and supplementary high speed tape senders. It is reissued to include the latest engineering information, remove the preliminary designation, and change this section to the standard format. Circuit description information formerly contained m Section 592-851-430TC can now be found in this section under theory of operation. The changes include certain pushbutton circuit breakers in place of toggle type, an added circuit ground terminal strip and an added tape reader motor switch and fuse. Since this is a general revision. marginal arrows that indicate changes have been omitted.

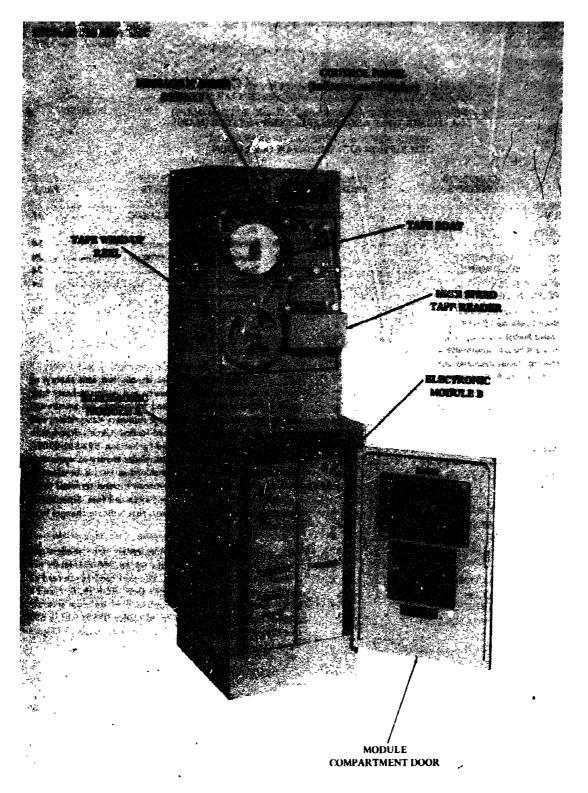

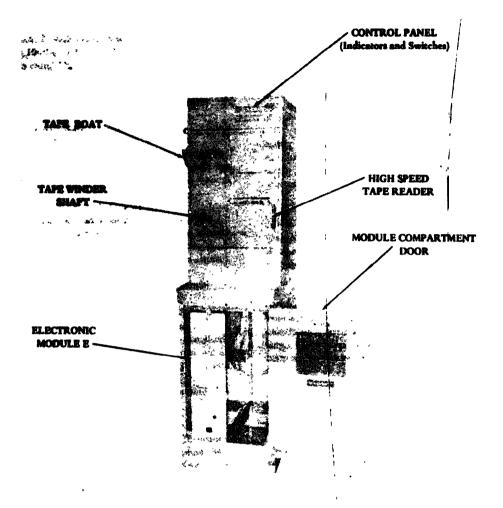

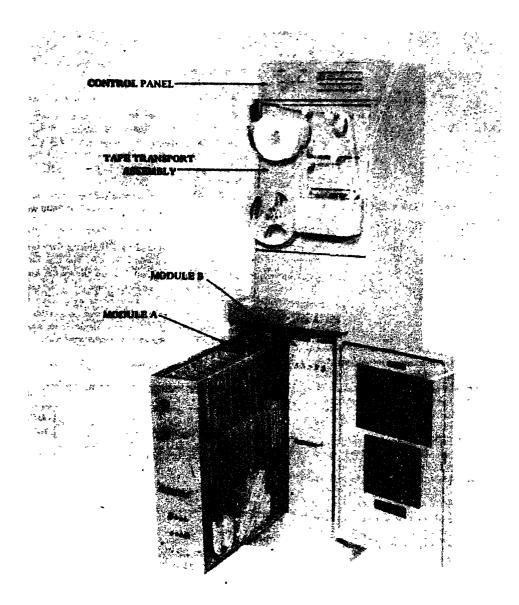

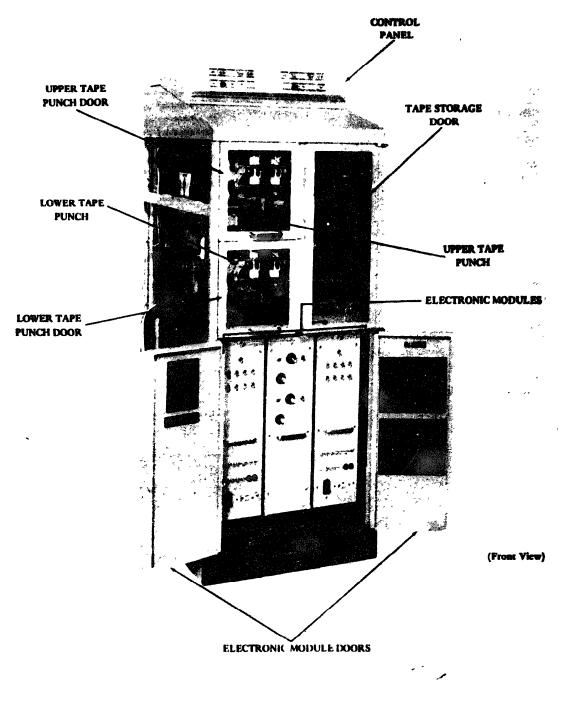

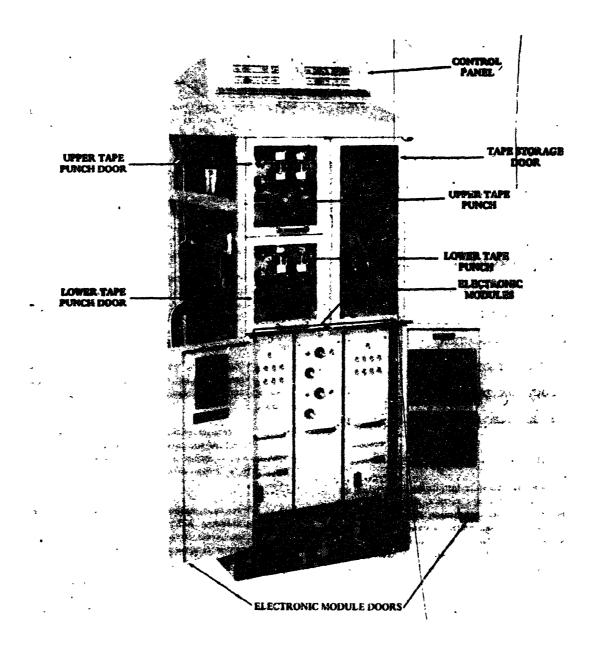

1.02 The master and supplementary tape senders can send messages at rates up to 240 characters per second (2400 words a minute) The tape senders can read all standard paper tape including one inch width (5. 6, 7, and 8 level). Each tape sender is contained in US own separate cabinet incorporating a high speed reader (DX2) with a 600 foot tape supply container and tape wind-up facilities (Figure 1 and Figure 2)

#### 2. DESCRIPTION

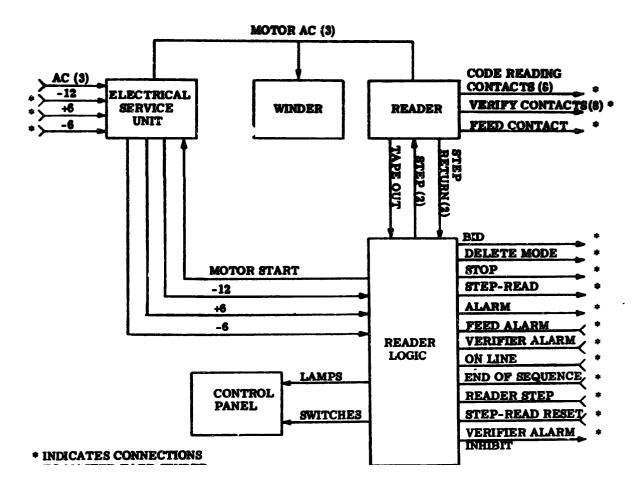

2.01 The master tape sender controls up to five supplementary tape senders and consists of a cabinet, cape reader, tape transport, and logic modules A and B. Logic circuitry includes reader control. drive circuits, message numbering, reader contact verification, feed verification. parallel to serial converter, and reader sequencing logic for controlling operations of the master and supplementary tape

1966 and 1969 by Teletype Corporation All rights reserved Printed in U S A

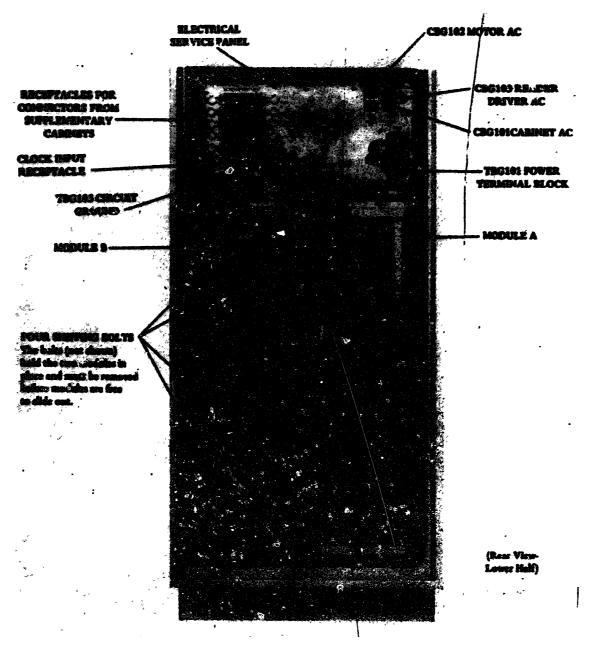

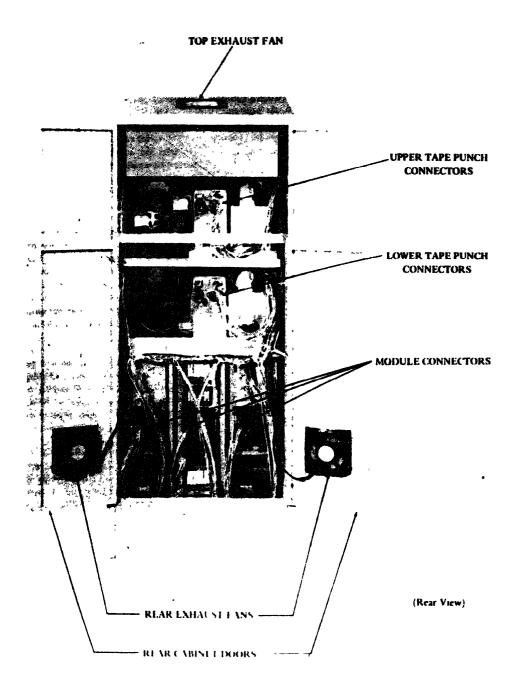

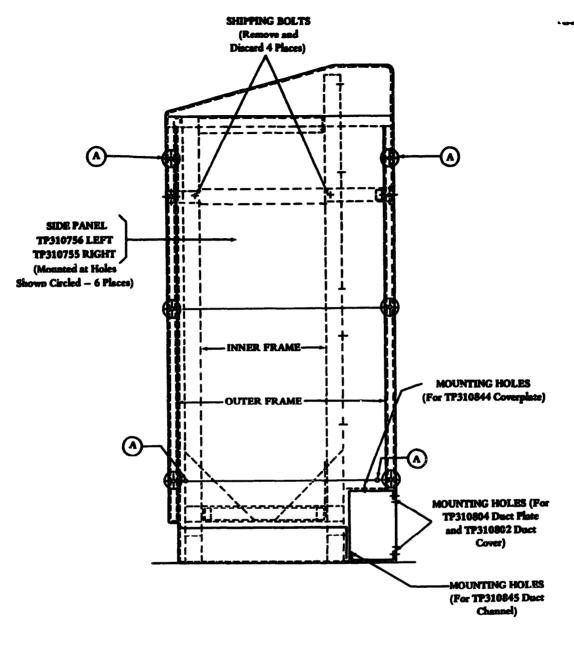

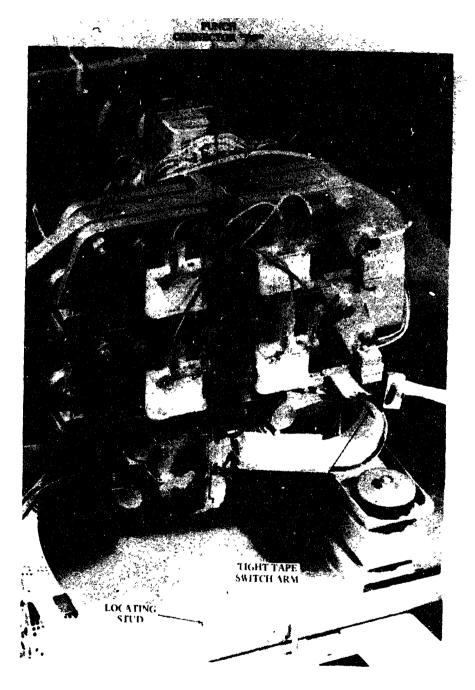

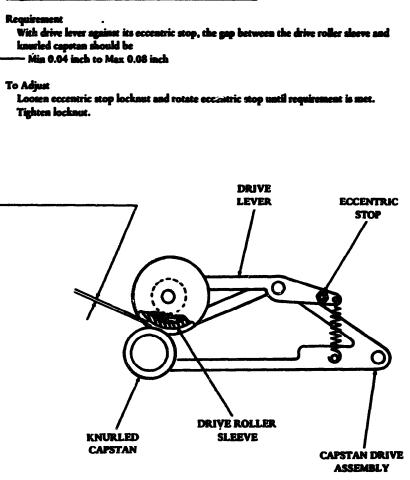

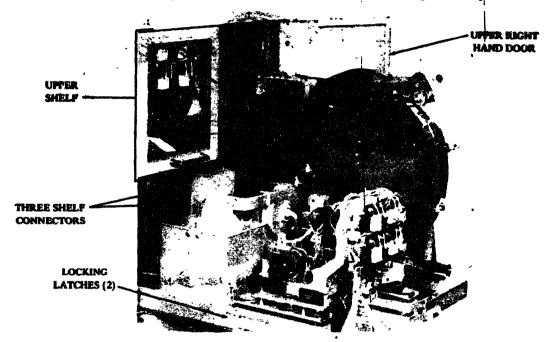

Figure 1. Master High Speed Tape Sender

Page 2

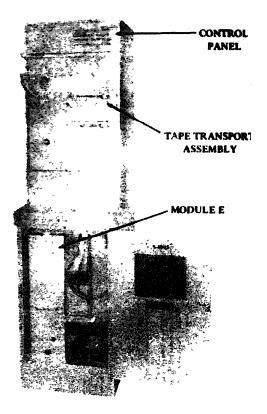

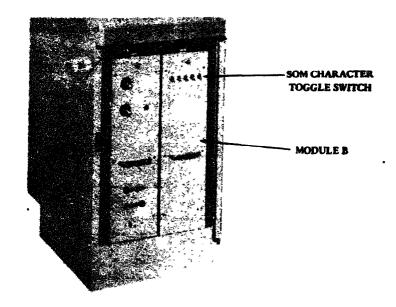

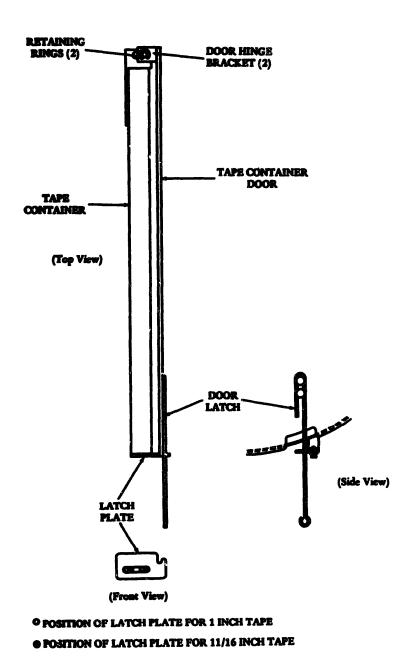

Figure 2- Supplementary High Speed Tape Sender

aunders. The reader sequence logic circuitry permits each sunder to transmit in turn one at a time, before any one sunder can transmit a second time (Figure 1).

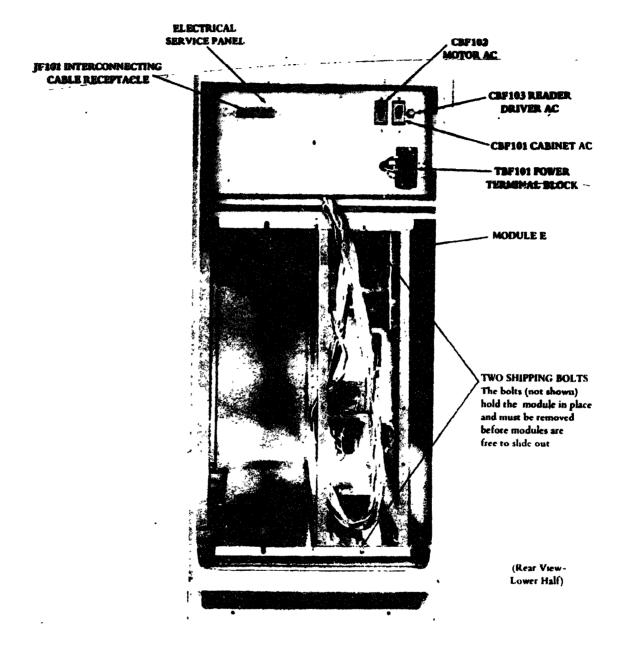

2.02 The supplementary tape sender contains the reader control and drive chronics for its associated tape masker. All other necessary logic circuitry is contained and controlled in the master tape sender cabinet. The reader toquence logic permits readers with tape to transmit in turn, permitting each reader to send before any one reader is given a second opportunity to send (Figure 2).

2.03 Each character is read and verified by the high speed reader, then sent by bit to external equipment Reader verification detects reading errors to **assure** that **deta** is delivered correctly to the parallel to serial converter

A message numbering circuit automatically inserts a message number sequence ahead of each transmission.

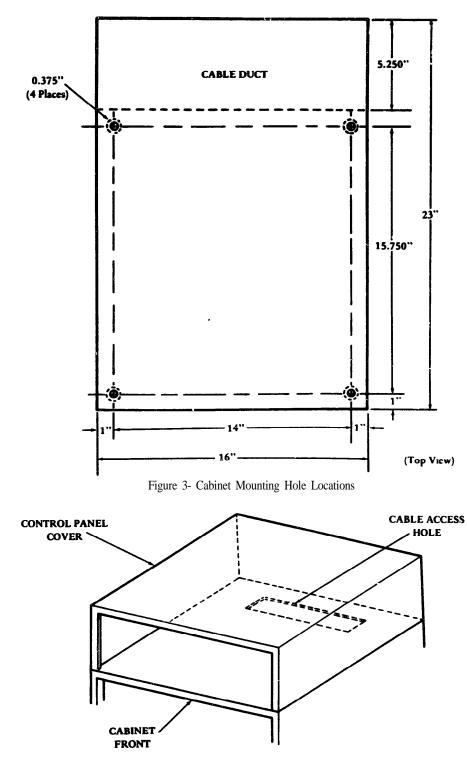

2.04 The master transmitter and supplementary tape senders are mounted in separate cabinets. Each cabinet is 16 inch wide 23 inches deep, and 60 inches high. Tape readers. tape handling mechanism, electronic logic, and power supplies are accessible from the front of the cabinet. Component connections and some maintenance can be performed through the rear cabinet doors.

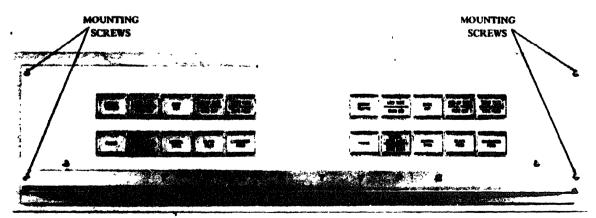

2.05 All controls and message numbering display (on master cabinet panel) are located on the control panel at the top of each cabinet The logic circuits are mounted on removeable plug-m type etched circuit cards, for case in replacing components and maintenance

#### ASSOCIATED EQUIPMENT

# 2.06 The master and supplementary cabinets contain a tape transport and tape reading equipment. After the tape is taken up through the tape transport system to a power driven tape reel. Tape is read in one direction only.

2.07 Reading is controlled by introducing drive pulses to the high speed. tape reader, which results in feeding the tape one character for each drive pulse. Drive pulses and output signals must conform to the specifications outlined in Section 592-804-500TC.

2.08 Sender operation begins by replacing a tape in the reading head of the master or supplementary reader and operating the BID switch. When no other sender is transmitting, the message numbering sequence to immediately sent and the reader starts operating

2.09 The data information is delivered by the reader to the parallel-to-serial converter of the master sender in parallel wire form. It is converted to a serial pulse stream and delivered to external equipment at appropriate signal levels. Data information may be delivered **to** external equipment directly in parallel form.

#### TECHNICAL DATA

A. Temperature and Power Specifications

2.10 Operating temperature fop all cabinets and equipment is between 40 degrees to 110 degrees fahrenheit ambient room temperature. Humidity ranges are between 5 percent and 95 percent for best operating efficiency. The power supply. located in the master sender cabinet, furnishes voltages for logic circuitry in the supplementary sender cabinet as well as the master sender. Reader stepping power is supplied by each individual cabinet. Power requirements for the master and supplementary cabinets are as follows.

- (2) 117 volts ac  $\pm 10\%$ , 58.5 to 61.5 hertz, single phase.

- (b) The master cabinet uses 287 watts without any supplementary cabinets connected; and 362 watts with five supplementary cabinets connected, transmitting a test message.

- (c) Each **supplementary** cabinet uses 208 watts transmitting **at** 2400 words per minute.

B Input Signal Requirements

2.11 Input signal voltages are nominally positive and negative 6 volts  $\pm 1$  volt. The minimum input impedance for all signals is mote than 5000 ohms. Input

signal capacitance is less than 0.0025 microfarade, and maximum input operating current of 0.0001 amperes. Input circuit switching occurs between the limits of ±0.5 volts or less.

#### C. Input Signal Characteristics

2.12 Input signals from a binary timing clock controls the transmitting bit rate. This square wave signal with +6 volts and -6 volts has a bit rate exactly twice the data bit rate. The positive leading edge of each clock pulse occurs in time with the beginning of each binary data bit.

2.13 An abnormal traffic input to the master tape sender. controls a red warning indicator on the control panels of the master and supplementary tape senders. A -6 volt signal will operate the indicators and +6 volts will turn them off.

D. Output Signal Requirements

2.14 The output voltage of all signals is +6 volts  $\pm 1$  volt or -6 volts  $\pm 1$  volt, and the source impedance of the signals should not exceed 100 ohms. The maximum short circuit current delivered to the Interface should be 0.1 ampere.

#### E Output Signal Characteristics

2.15 The serial data output is a positive and negative 6 volt binary stream, The character rate is under control of the incoming clock signal and should not exceed 240 characters per second. Each character incorporates from 5 to 16 bits for synchronous operation, or from 6 to 16 bits for start-stop operation. The start bit of every start-stop character is generated at the same polarity (+6 volts or -6 volts), this is used to maintain character synchronization by the external equipment.

2.16 The next bats of each character (5, 6, 7, or 8

depending on mode of operation) carries the variable message information, while the remaining unused bits are transmitted marking (+6 volts). The synchronous signal contains no synchronizing information during data transmission because it contains no start bit. With no data being sent, a synchronizing pattern is generated under control of the timing clock input. This pattern is used by external equipment to achieve character register. any unused bus are always transmitted marking (+6 volts).

2.17 A parallel wire output IS available for 5, 6, 7, and 8 levels, corresponding to the 5, 6, 7, or 8 channels of the input tape. The signal output corresponding to the punch in the tape should be +6 volts; with no punch in the tape, the signal output should be -6 volts. Signals present for the entire character duration, less 200 microseconds at the end of the character.

2-18 nel clock output defines the al is present it is -6 volts cter. of the B ( ipe (11/16 in els . 0 enting wit ht will be marking. When : (7/8 is upe (1 inch), level eight will be

#### MASTER TAPE SENDER LOGIC

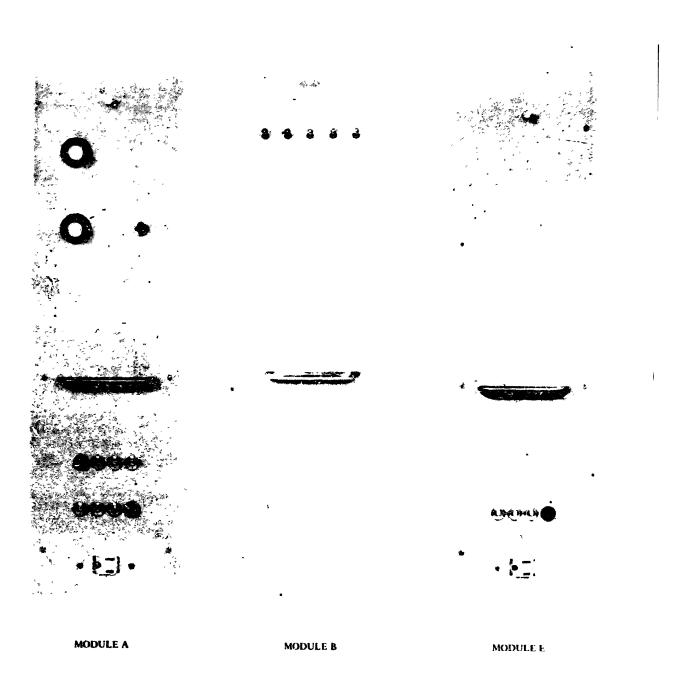

#### A. Modules

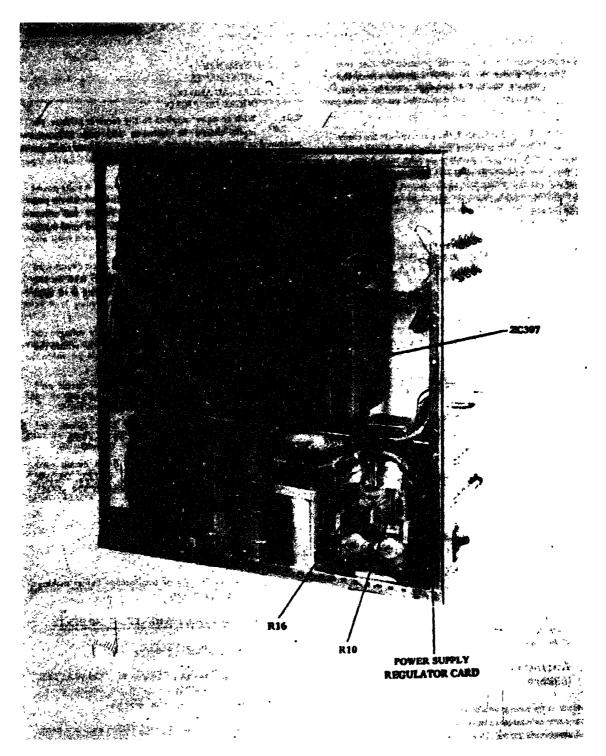

2-19 The electronic logic d located in B) a (E) is used in the i inch of a e with a 86

2.20 The electronic components are mounted on etched circuit plug-m cards. Each module can be fully extended or removed from the cabinet for ease of testing and maintenance. The converting cables at the rear of the modules provide enough slack to permit module removal without disrupting service.

#### B. Modules A and E

2.21 Reader control and drive circuits contained in both modules A and E, includes circuits that will accept low level reader drive signals from the sequencing logic, and converts them to high power pulses to drive the reader. There circuits also perform miscellaneous alarm and control function peculiar to each cabinet, and are incorporated in all supplementary and master cabinets.

2.22 The parallel to serial converter circuit (shared by all associated supplementary tape senders) accepts a parallel input signal and converts it to a serial signal output. The serial output is 5 to 16 bits for synchronous operation, or 6 to 16 bits for start-stop operation to define a character. The mode is selected by the SYNCHRONOUS START-STOP switch on the front of the module.

2.23 In the synchronous operation, the first 5, 6, 7, or 8 bits define the character and the remaining bits are always transmitted as marking bits (+6 volts). The fat bit in the start-stop operation is always transmitted the same (either mark or space according to the program), the next 5, 6, 7, or 8 bits define the character. The remaining bits are always transmitted as marking.

2.24 The bit levels and signal sensing are programmed in that, the signal sensed by the reader in one channel may be programmed for transmission in a different bit position. A signal sensed as a space, may be programmed for transmission as a mark.

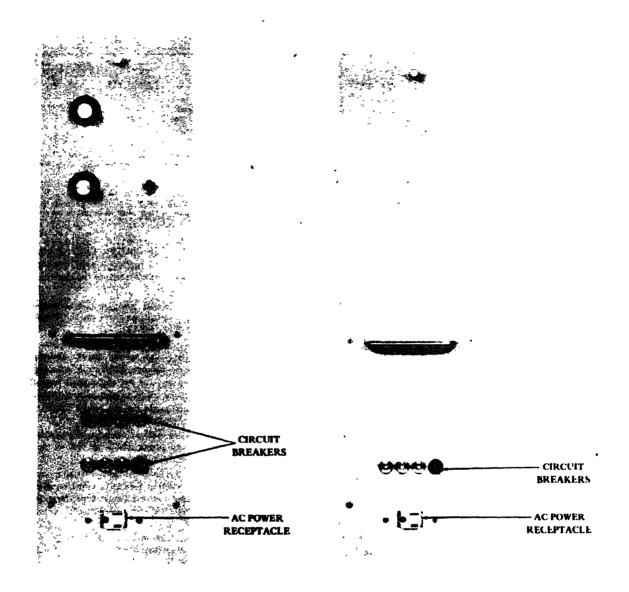

2.25 Circuit breakers are provided at the power supply output for over load protection. Should a circuit breaker trip, the normal procedure of turning off cabinet power prior to resetting circuit breakers should be observed.

#### C. Module B

2.26 The ruder sequencing circuit controls the operation of the master and supplementary tape senders. Since all associated readers share this common logic, the circuit direct reader drive signals to the proper reader, and only one reader may send at **a** time. The circuit also prevents any one reader from sending a second time until all readers have had the opportunity to send first.

2.27 The message numbering circuit is a visually displayed control circuit on the master cabinet control panel. This message numbering device is capable of operating with supplementary as well as with master senders.

#### Page 6

## The visually displayed numbers during message transmission, or during idle time, is the next number to be sent.

2.28 Each reader transmission is preceded by thirteen characters. These consist of: seven programmed identifying characters, one operator programmed character, one figures character, three numeric characters, and a letters character in that order (example: ZCZCABCX/999/). The three numeric character **increase one count after each** transmission. The counter can be manually reset to any count **including zero. The operator has the option of deleting** complete sequence by use of the NUMBERS DELETE switch. The message rate is limited to the maximum recycling rate of the counter (five times per second).

2.29 The reader contact verification circuit (shared by all readers) compares information presented to the parallel to serial converter with the actual character punched **in the tape.** Each character is read by two functionally independent contact reading assemblies, and the outputs compared. If one output does not match the other output, **a** reading failure is assumed to have taken place and the verifier alarm circuit is energized. Tape motion is verified by a sensing contact, which reads each feed hole as the tape passes over the tape feed wheel.

#### D. Alarms

2.30 When a condition occurs requiring immediate attention, the specific cause of each alarm is indicated by illuminating the affected control switch in red on the control panel of the appropriate supplementary cabinet and master cabinet. An alarm will be activated if the verifier detects an error or if a reader fails to feed. Alarm indicators must be reset manually, even when the alarm condition corrects itself. When an alarm is activated, a transfer contact (common to all alarms) in the master cabinet operates and is made available to the external apparatus.

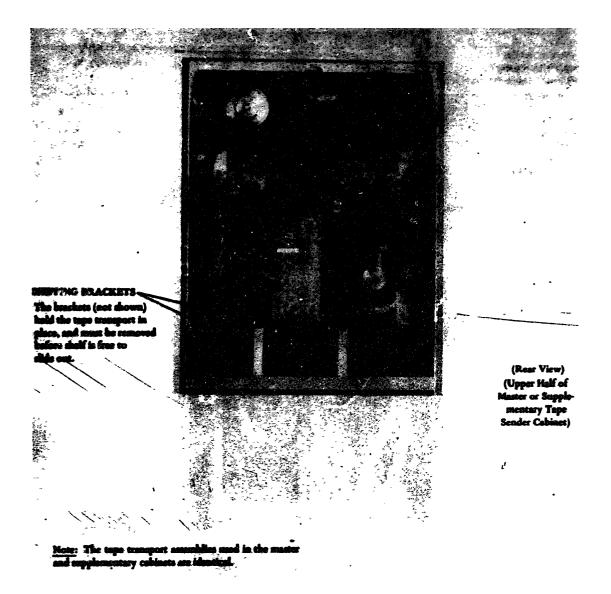

#### TAPE TRANSPORT MECHANISM

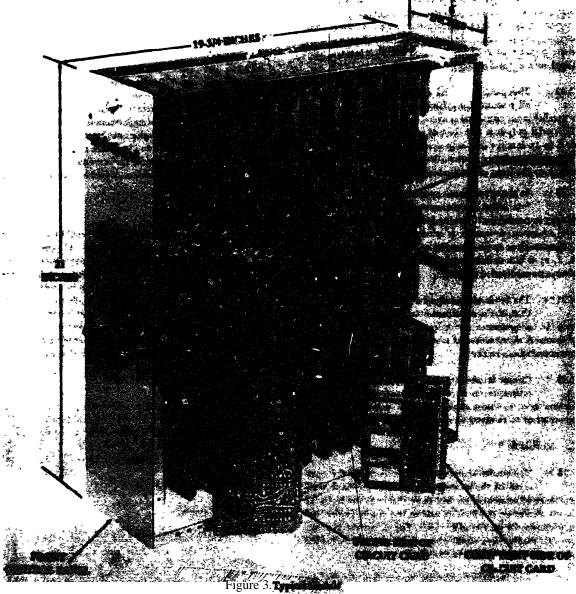

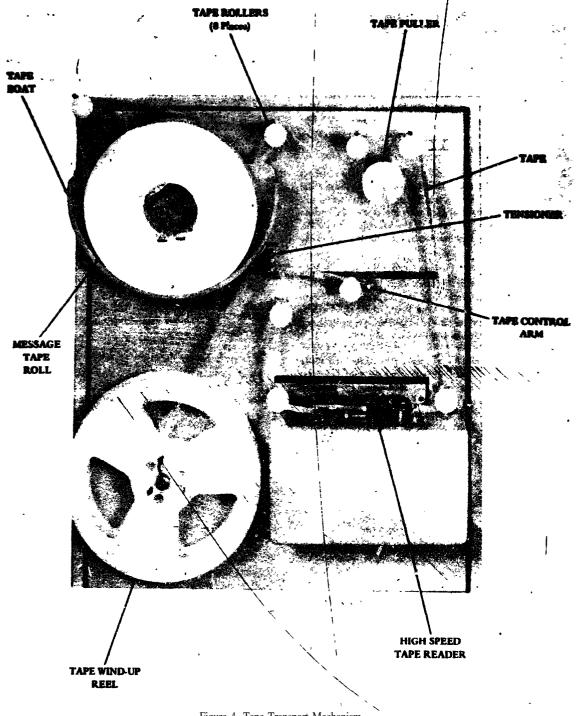

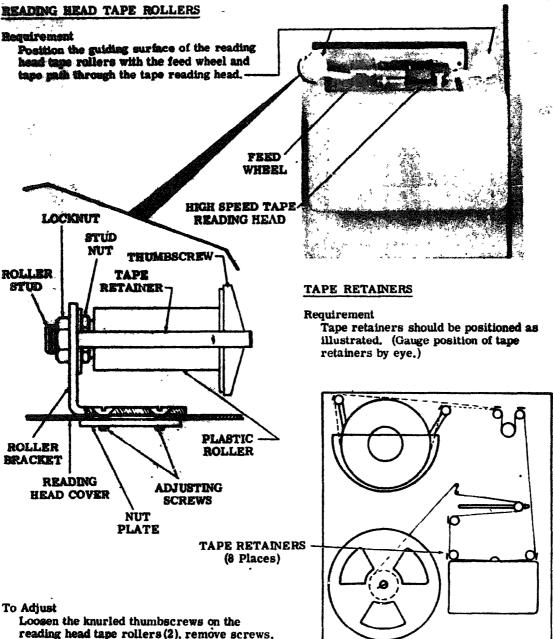

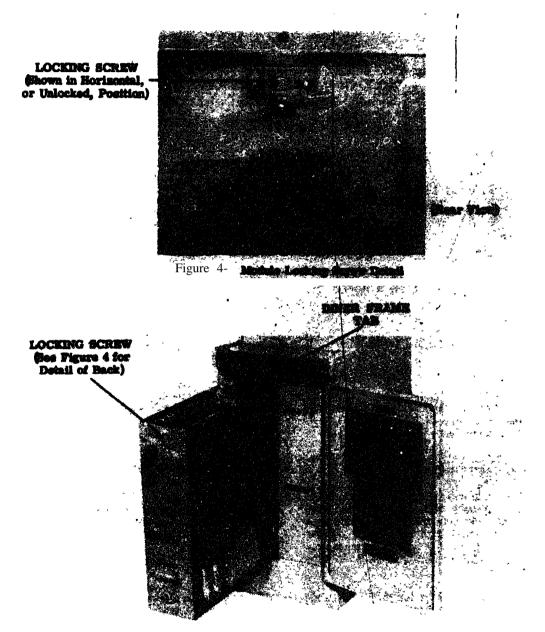

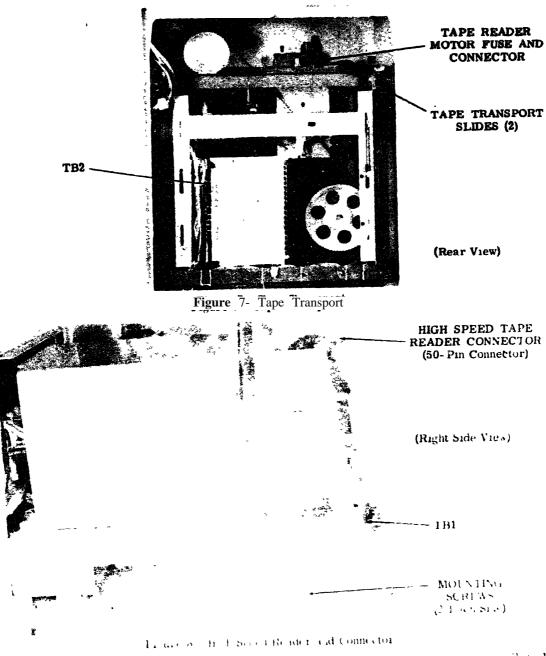

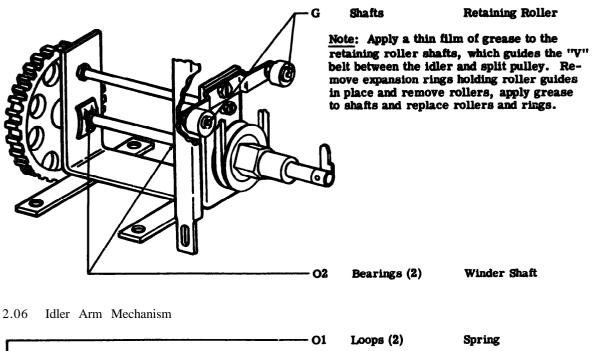

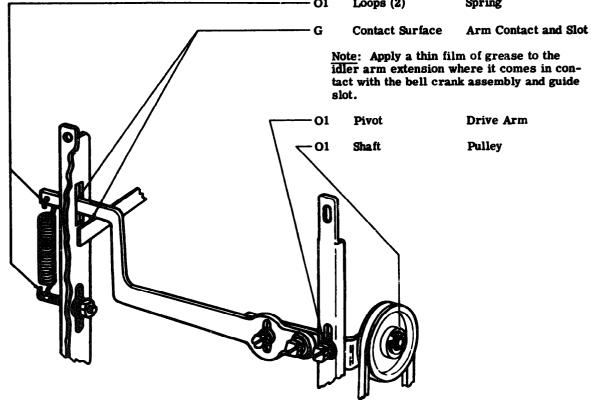

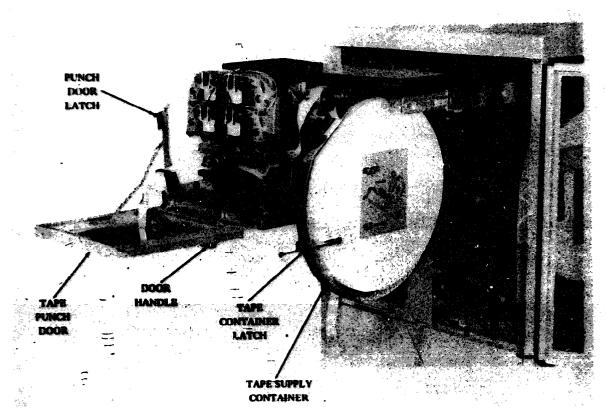

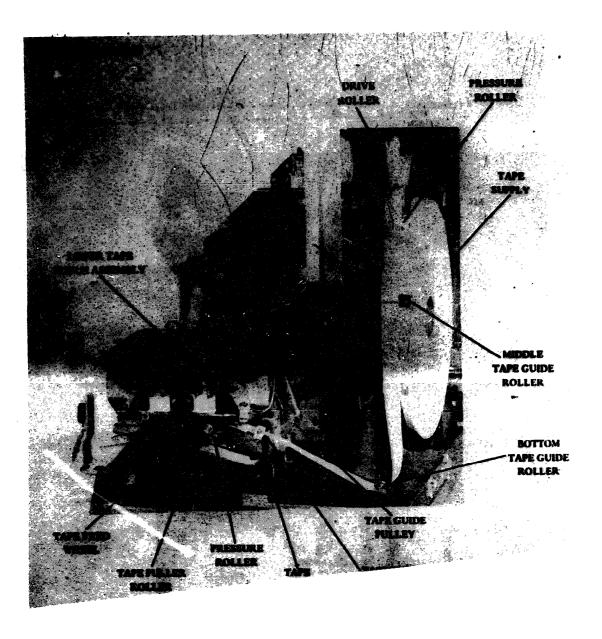

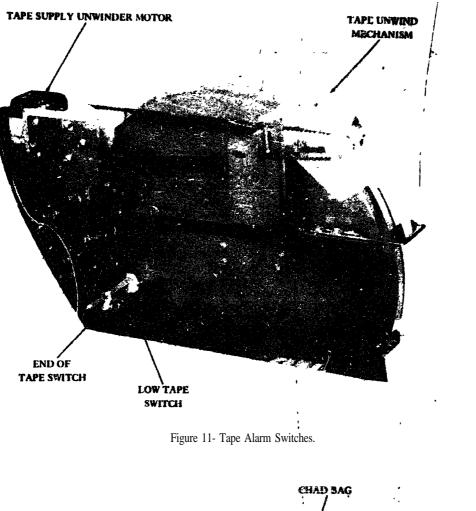

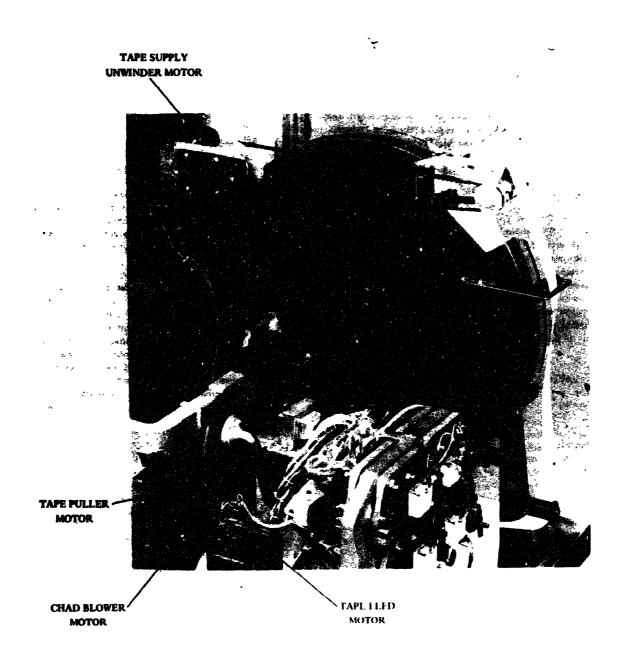

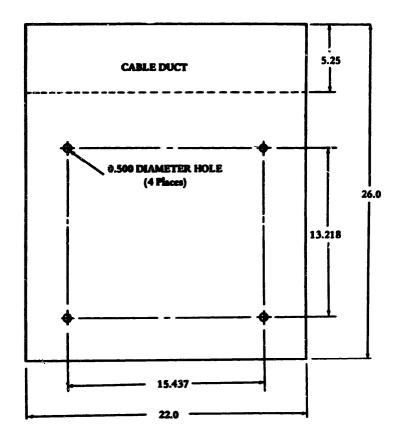

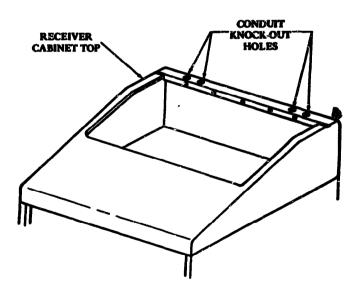

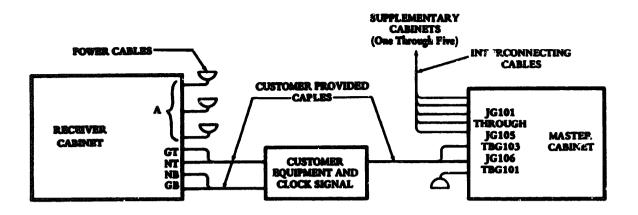

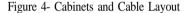

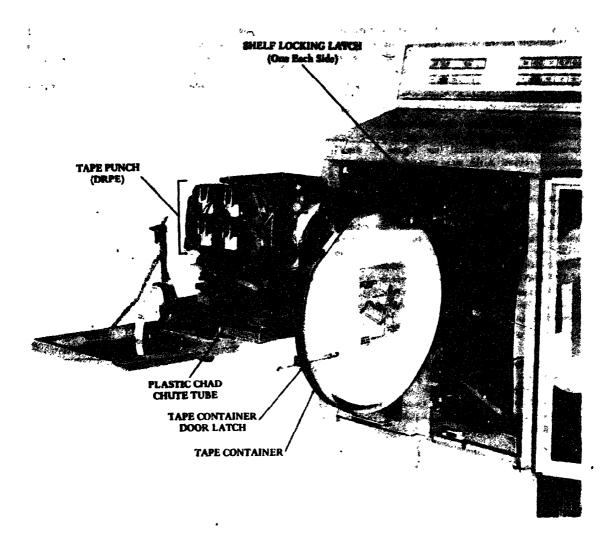

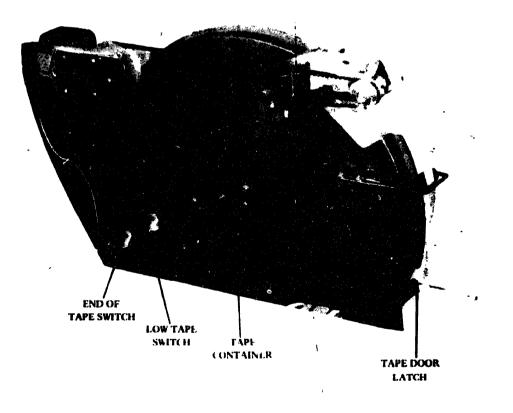

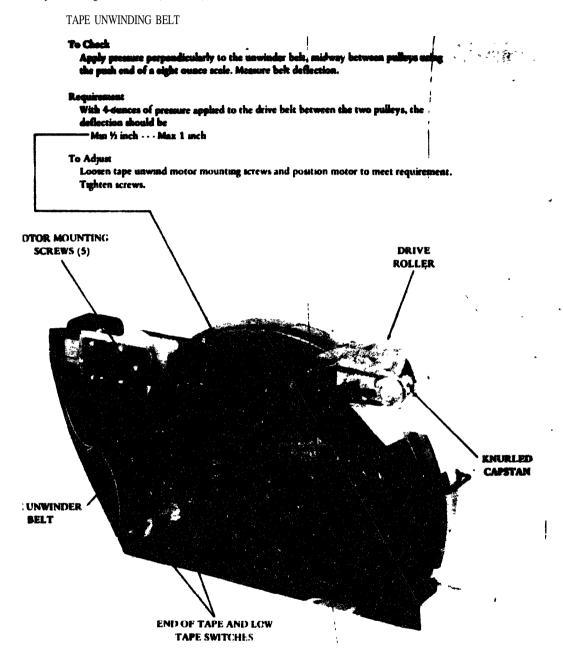

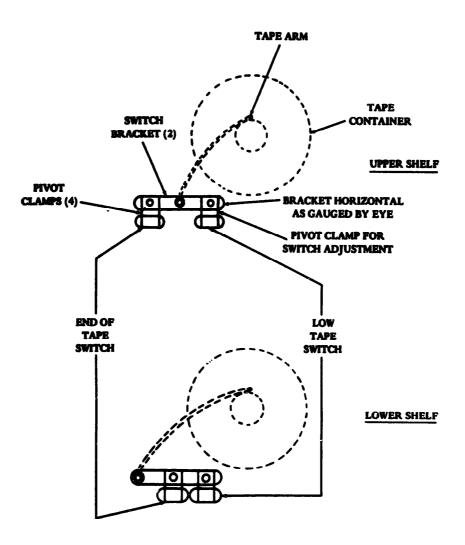

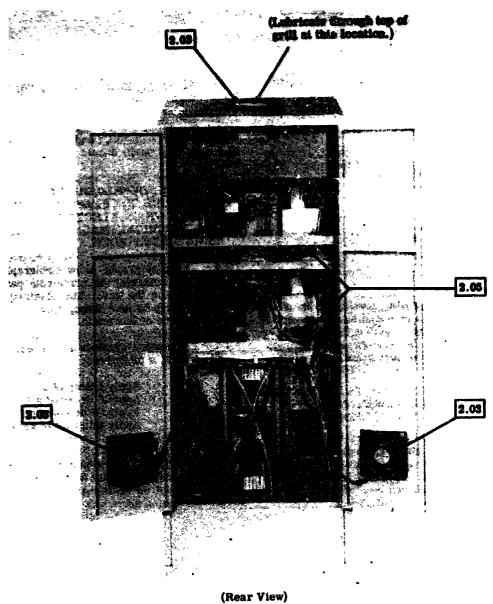

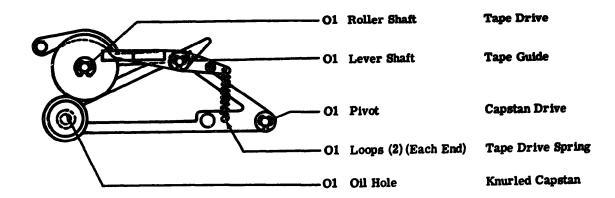

2.31 The tape transport mechanism provides tape handling facilities for the high speed tape reader. The mechanism mounts in the supplementary or master cabinet, the dimensions are, 14-3/4 inches wide, 18 inches high, 19-1/2 inches deep, and the weight is 31 pounds. Tape supply is approximately 700 feet and tape winder capacity is approximately 900 feet (Figure 4).

#### TAPE THREADING

2.32 The message roll of tape is placed in the tape boat with the three hole side closest to the panel.

Unwind approximately five feet of tape for threading through the tape transport system. Thread the tape along the path indicated on the label located on the plastic cover of the tape boat. Wrap approximately two turns around the wind-up reel hub to insure a nonslip start (Figure 4).

Figure 4- Tape Transport Mechanism

#### 1-14 SECTION 592-851-130TC

2-33 If the loose end of the tape roll is on the left side of the tape boat, run the tape over the left tape roller. Run the tape over the right tape roller if the tape end is an the right side. Pull the tape over the roller to the left tape puller roller, place the tape over the puller roller and the tave puller and then over the right tape puller The tane puller rotates continuou ily, but only ed around the puller from a it is tight a created by the high speed reader (DX). The tape then n the right idde of the p el and un hand tape roller on the high speed tape reader of the tape in the reads

2.34

threading from left togright and around the tape control arm either. College a horizontal path with the tape to the bottom into transferer, bring the tape up the left side and over the tight side of the top tipe transferer, then run the tape to the window rock.

2.55 Then the one because shock between the realise and the explosion, the encoded are moved the regime Hampie appears of levers, the best clottels to the regime appears of levers, the best clottels to the regime to the set for the best clottel.

2.56 The high against store number (DN) driver and power supply provides. 28 only and 46 yoks operating taking to a deal adaptive driver and assembly. The deal supplies driver charges the low lower supplies policy to a power level adequate for exemploing the seader suppling calls. Refer to Section 592-004-1907C, for high speed tape reader information.

#### 3. THEORY OF OPLRATION

#### CONTROLS AND INDICATORS

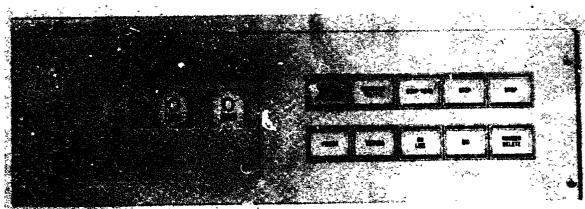

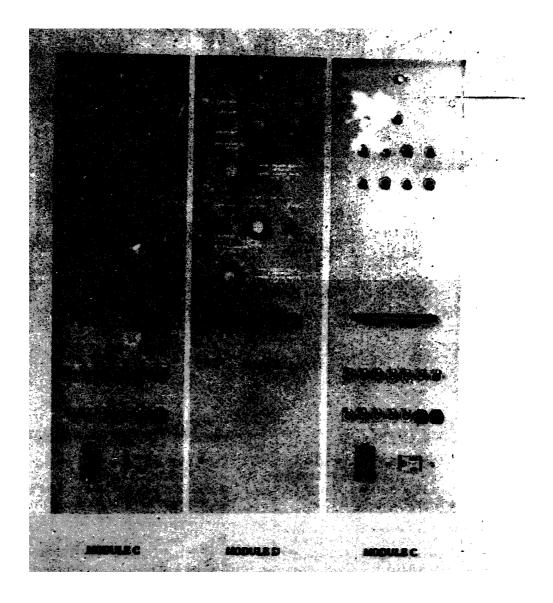

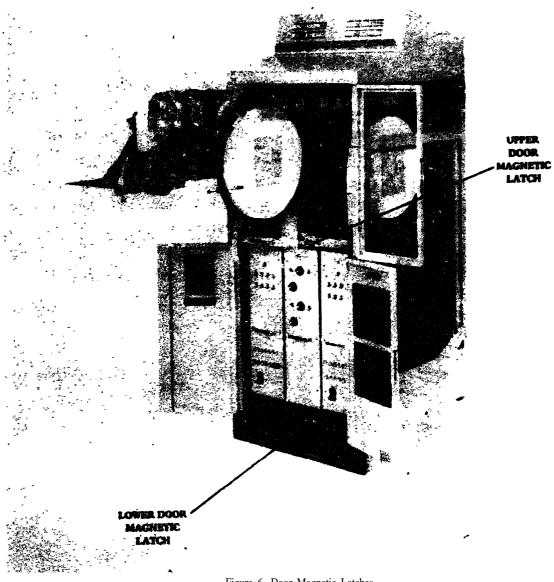

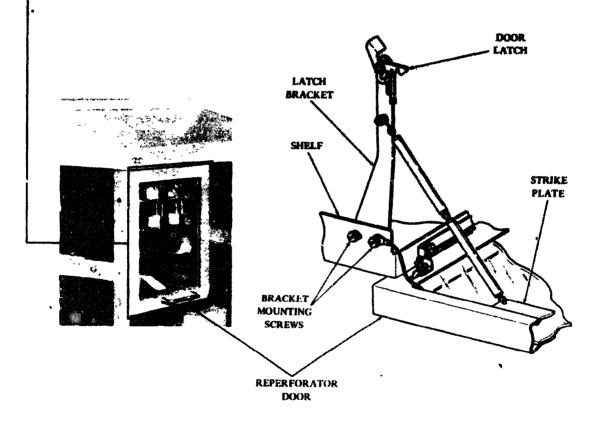

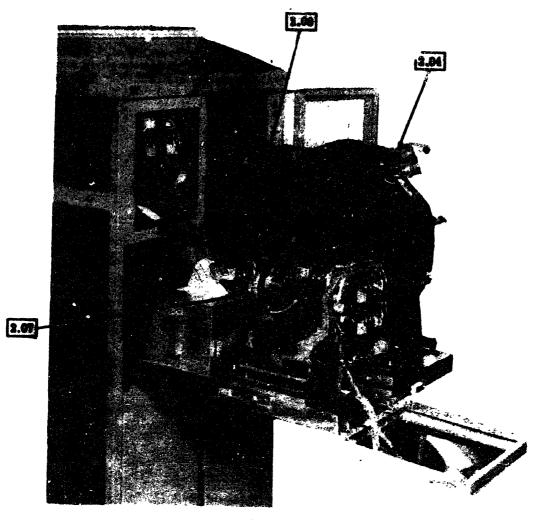

3.01 Operator controls and indicators are located on the control panel at the top of each cabines the master and supplementary control panels are identical to the message numbering indicator on the left side of the message numbering indicator on the left side of the message numbering indicator on the left side of the second panel. Additional cost of the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic modules is the located front panels of the electronic module (Figures 5, 6 att 7).

3.02 The VERIFIER/TAPE FEED Regimes 2 with split alarm and pushbutton split has alarm in red, with the reast switch common for External equipment alarms are accepted draw common to both alarms, providing the alarms contacts.

3.03 The ABNORMAL TRAFFIC indicator to the internal traffic input signal is decided over the external equipment.

3.04 When the reader is in the GTOP compared with the STOP READ switch can be used to stop the through a tape message, one character length (0.1 1) is each operation of the switch. The operator may use the tape switch to manually step the reader at times when there is as normally supplied step pulses.

Figure 5-Master Control Panel

Figure 6- Supplementary Control Panel

3.05 Opposing the SEOF emisch, flourisates the switch indicator and apposite roader during transmission. No other exception wider stop scale of this time. Opposing the switch a monthl time, puts out the switch light, and restarts the media and tipe studing system.

3.06 When the FOURTH output is operated, the emitch indicator is flowingtid and the switch settings electric power to the time generators motor, tage stadar meter, and electronic indicate.

3.07 When a life its suscept has not been initiated, operate the MOVERS which, which illustances the indicator and garmits suscent operation of the reader and tape winder motors.

3.08 The ON LINE indicator is illuminated when the soulier has authorization to transmit.

3.09 The BID switch indicator is illuminated when oparated and generates a bid to transmit when tape is in the surder.

3.10 When the MUMMER DELETE which is operated and liberingsted, the start of manage sequence is not transmisted about of each transmission. At the end of, each transmission the switch automatically result to the matural (and running) made and the indicator light is transid off.

3.11 Chronit businesses provided on the fourt pixel of the participality standals for overland provident.

Shandi a cissuit basilin pip so its off positing, the temperpositions of standay off calduct power before standing the lighter description descript. 3.12 The additional controls tound on the front panels of the electronic modules in the lower half of the additional controls in the lower half of the

(1) Module A - CODF I EVEL selector switch (5, 6, 7, and 8 levels). UNITS PER CHARACTER BE TERVAL selector switch indicates synchronous or state-stop level numerals; SIGMAL MODE toggits switch indicates either START-STOP or SYNCHRONOUS operation

(2) Module B - The SOM CHARACTER soggle switches (2, 3, 4, 5, and 6) one for each character bin, are operated in MARK or SPACE position to determine the eighth character in the start of message isoquence.

(4) Module E - The module control panel contains some logic circuitry and logic voltage circuit invalues, all other controls are contained in modules A and B in the master cabinet.

CIRCUIT DESCRIPTION

3.13 The 0 volt, and -5 volts on some internal leads, are identified by a shaded corner in the logic symbol from which they originate. The dc coupled inputs to logic elements are shown as half arrow basds. Full arrow t and indicate ac coupled (pulse) inputs.

3.14 The commonly used NOR logic element is identified by the designation LA within the element symbol. The output of the element is manifered any toput is 6 web. The engine is 6 web calls if (i) is your of negative A special input Mandfield by in conversion and conter of the symbol, allows the addition of some light.

1-16 SECTION 592-851-130TC

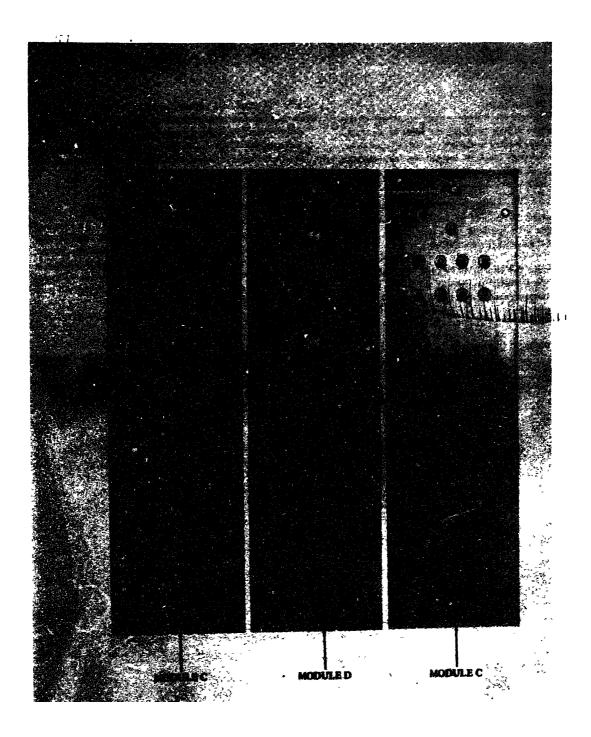

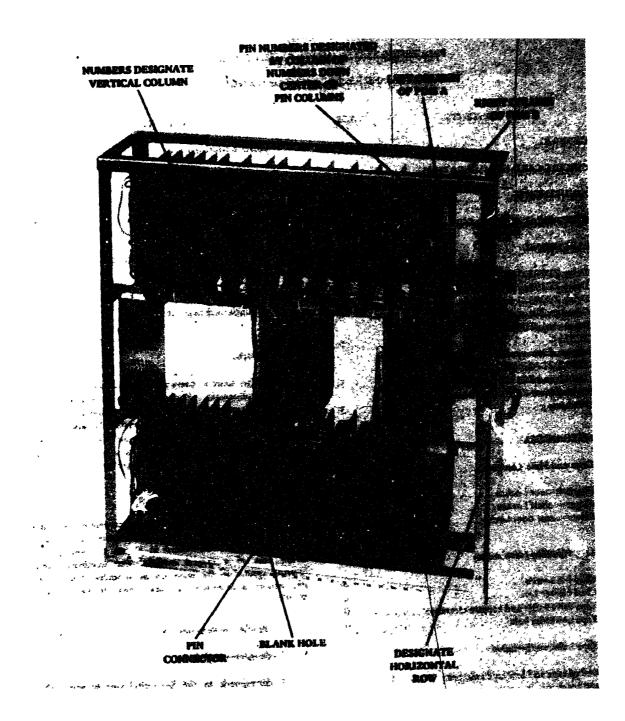

Figure 7- Master and Supplementary Modules

inputs to the element, or connecting two or more elements together to obtain more inputs and greater load driving capability.

3.15 The flip-flop element is designated by a rectangular box with a diagonal line across the lower half. The priming voltage inputs are shown as half arrows, and the actuing voltage inputs by full arrows. Prime one input arrows enter the upper half of the symbol, and prime 0 volt and set 0 signals enter the lower half of the symbol. An arrow extering the conter of the symbol designates the set 1 and set 0 inputs are connected together.

3.16 If no priming inputs are shown, the prime 1 input is connected to the inverted output (lower half of the symbol) and prime 0 input is connected to the normal cutput (upper half of symbol). Each input pulse reverses the condition of the voltages on the normal and inverted outputs.

3.17 The pulse amplifier element is identified by a square box with the letters PA in the symbol. A full arrow head indicates the input. This element produces a pulse approximately two microseconds in duration whenever the input goes negative. When both inputs are used, a pulse is produced only when both inputs go negative.

3.18 A trapezoid with the letters PA within the symbol represents the power amplifier element. This element has two inputs and can perform the NOR element function with approximately three times the load driving copability of an ordinary NOR (LA) element.

3.19 The delay element can be used either as a one shot or a free-running multivibrator, and is identified by a square box with the letters DY within the symbol. Delay elements used as one shots have the pulse duration indicated, when used as a free-running multivibrator, the frequency is indicated.

3.20 An input element translates input polar signals (+6 volts and -6 volts) to neutral signals (0 volt and -6 volts) used internally. It is identified by a rectangular box with INPUT printed within the symbol.

3.21 An output element tracalates neutral signals (0 volt and -6 volta) to output polar signals (+6 volts and -6 volta). It is identified by a rectangular box with OUTPUT printed within the symbol.

#### SUPPLEMENTARY READER LOGIC

3.22 The electronic logic circuits contained in module E are divided into the fellowing four functional groups: bid circuitry, start of message delete circuitry, step and read circuitry, and alarm circuitry. A. Bid circuitry

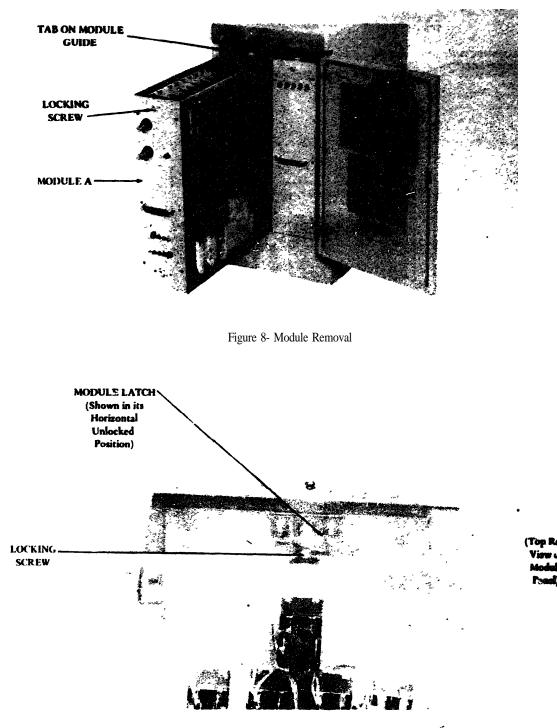

3.23 Insert the punched paper tape in the **reading head.** The normally closed tape-out contact moves to its open position which is connected to pin C8 of JE128. This action initiates the bid circuitry of the reader logic. Refer to 7711WD, Sheet 2, and Figure 8.

3.24 Pin C8 of JE128 assumes a negative voltage allowing the inverter ZE102 to saturate. The 0 volk output at the inverter (pin 9) is applied to the input pin B30, LA-2D, ZE103, and pin B4 of LA-2A, ZE118. AT LA-2D it is inverted, and applied to pin A32, LA-1D, ZE103 together with the input at pin B32. When both inputs are negative, the output on pin B34 is driven to 0 volt which acts as a prime voltage for setting the flip-flop D-B of ZE110 into the set one state. (Pin B33 is at 0 volt and pin B34 at a minus voltage.)

3.25 The BID indicator witch may now k operated to provide a transition at the input, pins A36, and B36 of flip-flop D-B of ZE110. The voltage transition switches the flip-flop to the set one state. The two LA networks connected between the BID switch and the complementary input are connected as a dc (direct current) flip-flop, to prevent switch contact bounce from affecting the set input of the flip-flop.

3.26 With flip-flop D-B of ZE110 in the set one state. pin B34 is driven negative and pin B33 is driven to 0 volt. The 0 volt is inverted by PA-1C of ZE108 and applied to PA-ID of ZE108. The output, pin B1 of PA-1D of ZE108 is driven to 0 volt, energizing relay K2 and the motor start relay K1 through an isolating diode CR3 of ZE110.

3.27 The diode presents relay K2 from king energized when the MOTORS indicator switch (SF107) located on the control panel, is operated Refer to 7710WD, Sheet 6 for the motor circuit. When energized, the motor start relay K1 starts the reader and tape winder motors. Energizing relay K2 lights the bid indicator lamp and motor indicator lamp. The diode connected between the bid lamp and motor lamp prevents the bid lamp from lighting when the MOTORS switch is activated.

3.28 The negative voltage at pin B34 on flip-flop D-B of ZE110 is inverted to 0 volt by PA-2C of ZE108 and applied to the input pin A32 on DY-A of ZE108 for a 500 millisecond one shot. The output pin A34 is driven to 0 volt and remains there for a period of 500 milliseconds, at this time it returns to a negative voltage. This negative transition is applied at the input pin A31 on PA-E of ZE108 and provides a positive pulse at the output, pin A27.

3.29 This pulse is again delayed by an identical delaypulse amplifier network. The results are a total delay of one second from the time a negative transition was obtained at pin B34 on flip-flop D-B of ZE110 until a pulse is 1-18 SECTION 592-851-130TC

Figure 8- Block Diagram for Supplementary High Speed Tape Sender

provided at pin B24 on flip&p D-C of ZE110. The associated prime input pin A24 on flip-flop D-C of ZE110 was driven to 0 volt at the time flip-flop D-B of ZE110 was initially switched by the BID indicator switch. The flip-flop D-C of ZE110 is switched, driving the inverted output pin B26, negative. This output is applied to the input, pin B25 on LA-IC of ZE114.

3.30 The second input of this element, pin A24, is supplied by the output on PA-1C of ZE108 which samples the normal output pin B33 on flip-flop D-B of ZE110. The normal output of flip-flop D-B, having been driven to 0 volt at the time the BID switch was activated, allows PA-1C section of ZE108 to provide a -5 volts to pin A24 on LA-1C of ZE114. With both inputs on LA-1C of ZE114 at a negative voltage, the output pin A27 is driven to 0 volt. This 0 volt is supplied as a BID request signal to sequence control logic in the master transmitter cabinet. 3.31 The effect of inserting tape in the reader and **operating the BID switch is to immediately start** the reader and winder motors, and one second later provide **a** BID request signal.

3.32 After operating the BID indicator switch, the operator may cancel the bid request provided action is taken prior to the receipt of the on-line signal from the sequence control logic. This reset action is accomplished by operating the BID indicator switch a second time to obtain a positive transition at the complementary input pin A36 and B36 on flip-flop D-B of ZE110. The prime 0 volt input at pin B35 of ZE110 is at 0 volt due to the input pins B22 and B23 on LA-2C of ZE114, both being negative. The input pin B23 was driven negative through PA-1C of ZE108 at the time flip-flop D-B first set.

3.33 The second input to LA-2C of ZE114 samples the on-line signal from the sequence control logic. As long as the on-line signal remains negative the flip-flop D-B of ZE110 is primed to be reset. When the on-line signal goes to 0 valk, the prime 0 volt input, pin B35 is driven negative and the equina for resetting the flip-flop D-B with the BID indicator switch is removed.

3.34 Flip-flop D-B can now be reset only by a tape-out indication from the reader. This tape-out indication is a positive transition at the input pin 12 of inverter ZE102 where it is inverted and applied to pin B4 on LA-2A, ZE118. If pin B5 on LA-2A is negative at this time a positive transition will be applied at pin B32 and pin B27 on supplementary gates of ZE110, resetting flip-flops D-B and D-C of ZE110. When these flip-flops are reset the reader and winder motors are turned off and the bid request to the sequence control logic is removed.

3.35 The negative input at pin B5 on ZE118 is a result of LA-2B on ZE118 sampling either an off-line **condition** or an end of sequence. If neither of these **conditions** exist the input at pin B5 will be at 0 volt and the tape-out indication will be prevented from resetting the **above mentioned flip-flops. This logic prevents an** incomplete **start of message sequence to be transmitted when** the tape lid is released during the sequence.

3.36 The power on reset circuit at position ZE202 is used to provide a collector set pulse to flip-flop D-B and D-C of ZE110, a predetermined time after power is turned on. This action insures that the bid circuitry is not bidding for the line when the equipment is initially turned on/ The 150 ohm, 1 watt resistors shown across the various relay contacts driving indicator lamps, are used to keep a small amount of voltage across the filament of the lamp. This reduces the initial current surge and extends the life of the lamp.

#### B. Start of Message Delete Circuitry

3.37 The number delete circuitry provides the operator with the option of deleting the number sequence which normally precedes each message tape. Prior to operating the BID indicator switch, the operator determines if the message tape requires a number sequence. If the number sequence is not necessary the NUMBER DELETE indicator switch is operated. This switch provides a positive transition at the input pin A36 and B36 on flip-flop D-B, ZE112, provided the on-line signal applied at pin B14 on LA-1B, ZE114 is negative. If this on-line signal is at 0 volt, indicating the associated transmitter is on-line, the indication from the NUMBER DELETE indicator switch is held at LA-1B of ZE114 and does not switch flip-flop D-B of ZE112. Refer to 7710WD, Sheet 3.

#### 3.38 Assume the on-line signal applied at pin B14 on LA-1B of ZE114 is negative and the signal from

the NUMBER DELETE indicator switch is presented to input pin A36 and B36 on flip-flop D-B of ZE112. This flip-flop will be switched to the one state, diving the output pin B34, negative. The signal is applied to input pin A4, PA-2D of ZE-108, driving the output pin A1 to 0 volt, which energizes relay K4 and lights the number delete lamp though the K4 relay contact.

3.39 The negative voltage at pin B34 of flip-flop ZE112-B is also applied to pm B26 on LA-1F of ZE103. This element is held at this time due to 0 volt being supplied to pin A21 from the output B6 on PA-1C of ZE108 (refer to 7710WD. Sheet 2). When the BID indicator switch is operated, flip-flop D-B of ZE110 is switched as described in 3.25. A 0 to -5 volt transition is applied to pin A24 on LA-1C and pin A21 on LA-1F of ZE103.

3.40 The output pin A27 of LA-K, ZE103 is held **at** -5 volts due to the 0 volt present **at** input pin B25 and output pin B28 on LA-IF of ZE103 goes to 0 volt. The resulting positive transition at the output of LA-IF is used to set flip-flop DC of ZE112 into the one state, driving the output pin B26, negative. This voltage level is inverted by LA-ID of ZE114 and applied to the sequence control logic in the master cabinet as a delete mode signal.

3.41 At the completion of the message tape, a tape-out indication is received from the tape-out contact at the reader. This indication resets the bid circuitry as described in 3.34, and provides a negative to 0 volt transition at pin B6 on PA-1C of ZE108, (refer to 7710WD. Sheet 2). This transition IS applied to pin B32 of supplementary Bate ZE112, resetting flip-flop D-B of ZE112. With the reset of flip-flop D-B, the NUMBER DELETE indicator lamp is extinguished. On later sets, the reset signal for flip-flop D-B of ZE112 is obtained at pin B6 and A10 of power amplifier PA-1C of ZE106.

3.42 During normal operation (not in the delete mode) the output pin B33, on flip-flop D-B of ZE112, is at -5, volts. This is applied to the input pin B25 on LA-1C of ZE103, and permits the negative bid signal transition at pin A24 as described in 3.40. The inverted signal is passed to flip-flop D-C ZE112 as a set zero signal. This provides a -5 volt indication at the delete mode output pin F7 of JE128.

3.43 At the completion of the start of message sequence a negative going transition is received from the master logic at JE128, pin E7. The signal is inverted by LA-2E, of ZE118, and applied to pm B31 of the supplementary gate ZE112 as a reset signal for flip-flop Q-C of ZE112. This reset signal is allowed to pass, provided an on-line signal is present at the prune input pin A31 of the supplementary gate. When flip-flop D-C of ZE112 IS reset, the delete mode indication to the master logic is changed to 0 1-20 SECTION 592-851-130TC

volt. This permits the step pulses in the master logic to be diverted from the start of message generator to the associated reader.

#### C. Step and Read Circuitry

3.44 During reader operation, the operator has the option of stopping the reader and stepping it manually with the STEP READ indicator switch. When the STOP switch is operated, the associated STOP indicator lamp is list and a voltage level change from 0 to -5 volts is obtained at pin B4 on LA-2A, ZE103. The switch output is fed through a dr flip-flop configuration, similar to the circuit described in 3.25 to remove contact bounce. (Refer to 7710WD, Sheet 4.)

3.45 When the reader is operating, the on-line signal input at pin B5 of LA-2A, ZE103 is -5 volta. As a result of the negative level being applied to pin B5 of LA-2A, ZE103 and the level change from 0 volt to -5 volta at pin B4 due to the STOP switch, the output pin A9 is driven to 0 volt. The 0 volt is used as a reader stop signal to the master logic and as a prime voltage to flip-flop D-P of ZE110.

3.46 In the master logic this signal is used to inhibit the stop pulses to the start of message (SOM) generator or the reader, thereby stopping operation. The prime voltage applied at pia A2 of flip-flop D-F permits the positive transition appearing at the set input pin A1, to switch the flip-flop, driving the output pin B3, to -5 volts. The positive transition at the input, pin A1, is a result of operating the STEP READ switch.

3.47 The output pin B3 of flip-flop D-F on ZE110 is inverted by LA-2E on ZE116 and sugplied to the master logic as a step-read pulse. This pulse allows the reader to be stepped one character, and read by the reader to be transmitted on line, provided the stop switch is in the stop position. When the STOP switch is operated again, returning it to its normal position, the reader is stepped automatically by the incoming step pulse rate.

3.48 The reader may be manually stepped (off-line) during periods when the reader is not normally being stepped by the incoming step pulse rate. The STEP indicator switch output is fed to a dc connected flip-flop configuration, consisting of LA-1B, and LA-2B on ZE116. When the STEP switch is operated, a positive transition is obtained at the output pin A11 of this flip-flop and applied to LA-1B, ZE103 for inversion prior to being applied to the input pin B13 of LA-2B, ZE103.

3.49 If the second input pin B12 of LA-2B is negative at this time, the input at pin B13 will be inverted and appear at the output pin A11. The input level at pin B12 is 0 volt only when the STOP switch is in its normal position and at the time the on-line signal input at pin B23 of LA-2C, ZE103 is -5 volts. When this condition is met it is assumes the reader is normally being stepped by incoming step pulses and the manual step indications are held. 3.50 The result is, the STEP switch is available for manually stepping the reader at times when it is not reading cape and being stepped by pulses received at pin D10 on JE128. Assuming the input pin B12 of LA-2B, ZE103 is at -5 volts, the manual step pulses at pin B13 appear inverted at the output pin A11. Then the pulses are inverted twice by LA-2F, ZE103 and LA-1F on ZE116.

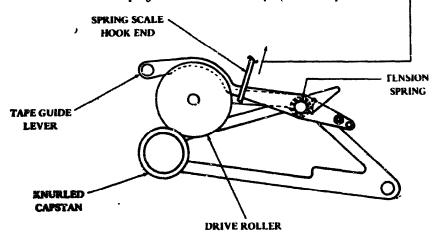

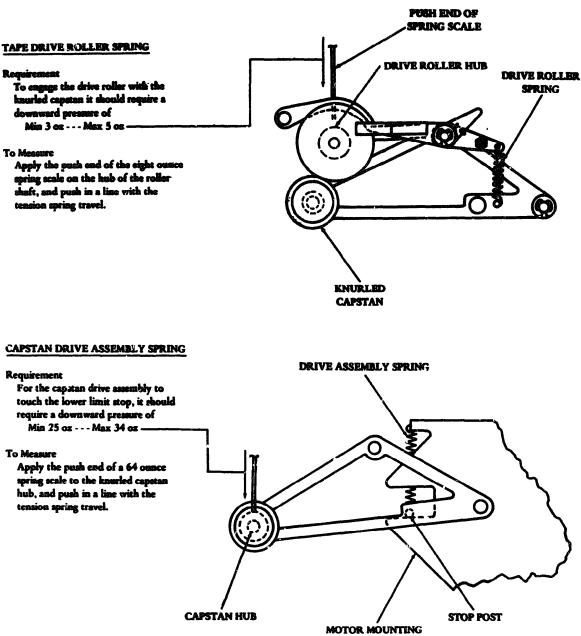

3.51 At the output, manual step pulses appear as positive transitions which are applied to the driver assembly. The driver assembly, located in the tape transport assembly, functions to change the low-level stepping pulses to a power level adequate for energizing the reader stepping coils. These pulses are delivered to the driver assembly from two sources, one from the STEP switch described in 3.50, and the other from the sequence control circuitry in the master logic. They are applied to pin D10 on JE128.

3.52 The LA-1A of ZE118 performs the function of preventing an alarm indication from occuring when the reader is restarted after it has been stopped and manually stepped with the STEP switch. This is required due to the characteristics of the verify logic explained in the following paragraphs.

3.53 Input pin A7 of LA-1A, ZE118 samples the condition of the STOP switch. When the STOP switch is in the stop condition, the input is -5 volts. Pin B7 of LA-1A, ZE118 samples the online signal, -5 volts, which is on at this point. The third input pin, A6 of LA-1A, ZE118 samples the STEP switch output at pin A17 of LA-1B, ZE103. When the switch operated, pin A6 of LA-1A, ZE118 is driven negative, with all three inputs of LA-1A, ZE118 at -5 volts. The output pin A10 is driven to 0 volt. This positive transition is applied to the master cabinet logic where it is used to prevent an alarm on reader start-up when the contacts are sampled again.

3.54 When power is turned off at the supplementary cabinet, relays K1 and K2 provide an open circuit at the stop signal output, pin C10 of JE128, and the step-read signal output, pin C9 of JE128. When power is turned on, the relays are prevented from energizing for a period of 80 millikeconds, after being energized, the contacts close. At this time the two outputs have had time to stabilize at -5 volts and any transitions are prevented from being applied to the master logic.

#### D. Alarm Circuitry

3.55 Two types of alarms are contained in the reader logic circuitry: A verify error alarm and a reader feed error alarm. When either one of these errors occur, an indication is received at pin A8 or B8 of JE128, setting an associated flip-flop D-D or D-E of ZE110. The flip-flops are primed by the presence of an on-line indication from the master logic. When either of the two flip-flops is set, an associated alarm lamp  $\neq$  lighted and a 0 web indication is applied at pin A1 or B1 c. A-27. (78103.) (2000) subput pin B9 of LA-28, ZE103 is inverted by  $\sum_{n \to \infty} E = 12$  (and supplied to the verifier in the master log).  $c \approx$  solt alarm signal. (Refer to 7710WD, Sheet 5.)

3.56 If the slarm flip-flops were to come up in the slarm condition when power is turned on, an output of the slarm circuix is required at LA-1C, ZE116. This prevenus an slarm indication to the master logic. Since an alarm at any one sender prevents operation at any other sender, this condition could interrupt the step pulses to an operating sender.

3.57 Press the VERIFIER/TAPE P\_D indicator switch (ALARM RESET on achematic) to reset a 2778 flip-flops and extinguish the alarm lamp or lot 28. 4 ON-LINE indicator lamp is lighted when the on-bit signal is received. The indicator lamp is a signal to the operator when a particular reader is allowed to transmit after a line bid has been entered. Relay K3 performs the same function at the output of the alarm circulary as relays K1 still K? performed in the step and read circulary described in 3.54.

3.58 The master transmitter cabinet contains one DX type reader with the necessary tape handling equipatent. The electronic logic and power supply is contained in two removable modules located in the lower part of the cabinet.

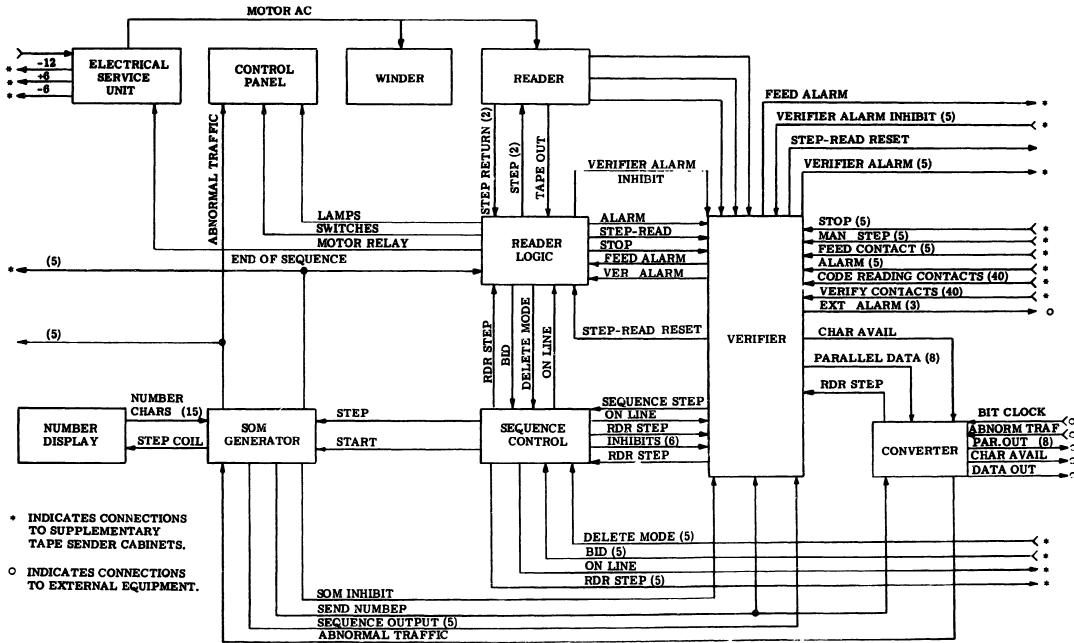

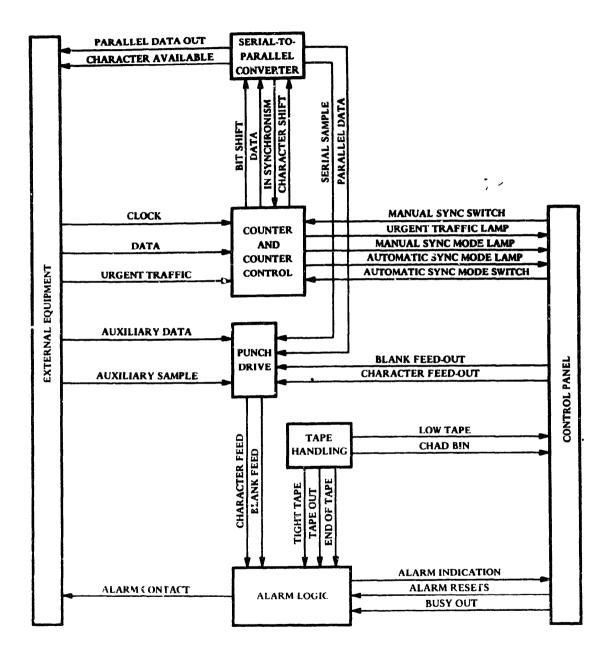

3.59 The electronic logic circuits in modules A and B are similar to the reader logic in module E and parforms the same functions described in 2.21 through 2.29. The controlling logic circuits contained in modules A and B are divided into five functional logic systems. They are arranged for controlling up to five external supplementary tape senders plus the associated master transmitter. Refer to Figure 9 for a block diagram. The logic circuitry consists of the following logic systems: reader logic, parallel to serial converter, sequence control, verifier, and start of message generator (SOM).

#### A. Reader Logic

#### **Bid Circuitry**

3.60 Insert the punched paper tape in the reading head. The normally closed tape-out contact moves to its open position which is connected to pin C8 of JA128. This action initiates the bid circuitry of the reader logic. Refer to Figure 9 and 7716WD, Sheet 2.

3.61 Pin C8 of JA128 assumes a negative voltage allowing the inverter ZA301 to saturate. The 0 volt output at the inverter (pin 9) is applied to the input pin B30 of LA-2D, ZA103 and pin A5 of LA-1A, ZA305. At LA-2D it is inverted, and applied at pin A32 of LA-1D, ZA103 together with the input at pin B32. When both inputs are magative, the output on pin B34 is driven to 0 volt which acts as a prime for the inputs at pins A36, and B36 for setting flip-flop D-B of ZA110.

3.62 The BID indicator switch may now be operated to

provide a transition at the input gans A36, and B36, of flip-flop D-B, switching to the set one state. The two V.A elements connected between the BED switch and the flip-flop set input are connected as a dc (direct current) flip-flog to eliminate contact bounce.

3.63 With flip-flop D-B in the set state, pin B34 is driven negative and pin B33 is at 0 volt. This 0 volt is inverted by PA-1C of ZA108 and applied to PA-1D of ZA108. The output pin B1, of ZA108 is driven to 0 volt energising relay K2, and the motor start relay K1 through an isolating diode, ZA110. This diode prevents relay K2 from being energized when the MOTORS indicator switch is operated. With the motor start relay K1 energized the reader and tape winder motors start. When relay K2 is energized the BID and MOTORS lamps are lighted. The diode (CRG101) connected between the BID and MOTORS lamps prevents the BID lamp from being energized when the MOTORS indicator switch is operated.

3.64 The negative voltage transition at pin B34 on flip-flop D-B, of ZA110 is inverted by PA-2C of ZA108 and applied at the input pin A32 of delay DY-A of ZA108. The output pin A34 is driven to 0 volt and remains at 0 volt for a period of 500 milliseconds, when it returns to a negative voltage. This negative transition is applied at the input pin A31, of PA-E on ZA108, and provides a positive pulse at the output pin A27. This pulse is again delayed by an identical delay circuit, the pulse amplifier network. This results in a total delay of one second from the time a negative transition was obtained pm B34. on D-B of ZA110 until a pulse is provided at the set input pin B24, on D-C of ZA110.

**3.65** The associated prime prime pin A24, was driven to 0 volt at the rime flip-flop D-B was initially set by the BID indicator switch. The D-C flip-flop is switched driving the inverted output pin B26, to -5 volts. This output is applied to the input Z25, of LA-1C, ZA-114.

3.66 The second input of LA-1C. pm A24 is supplied by the output of PA-1C on ZA108 which samples the normal output of D-B. The normal output pin B33, of D-B in driven to 0 volt at the time the BID switch is activated and allows PA-1C of ZA108 to provide -3 volts to the input pin A24 of LA-1C on ZA114. With both inputs of LA-1C, ZA114 negative, the output pin A27 is driven to 0 volt. This 0 volt is supplied to the sequence control logic as a bid request.

**3.67** The effect of inserting tape in the reader and operating the BID switch, is to immediately start the reader and winder motors and one second later provide a bid request to the sequence control logic.

3.68 After operating the BID switch, the operator may cancel the bid request by operating the BID switch a second time before receipt of the on-line signal from the sequence control logic. This reset action obtains a positive transition at the complementary input pins, A36 and B36 of flip-flop D-B on ZA110. A2 this time the prime one input pin, A35, is at -5 volts because the output pin, B33 on D-B, is at 0 volt. This 0 voltage is applied to the input pin, B32 of LA-1D, ZA103 driving the output of this element to -5 volts.

3.69 At the same time, the prime 0 input pin, B35, is at 0 volt because the input pins, B22 and B23 of LA-2C, ZA114 are both negative. The input pin, B23 was driven to -5 volts through PA-1C of ZA108 at the time flip-flop D-B was first switched to the bid condition. The second input to LA-2C, ZA114 is the on-line signal from the sequence control logic. As long as the on-line signal from the sequence control logic. As long as the on-line signal goes to 0 volt the prime 0 input pin B35 is driven to -5 volts and the ability to reset with the BID switch is removed.

7.70 Flip-flop D-B can now be reset only by a **reader** tape-out indication in the form of a positive transition at the input pin 12, of inverter ZA-301 where it is inverted and applied to pin A5 of LA-1A, ZA305. If pin B7 of LA-1A is negative, at this time a positive transition will be applied at pins B32 and B37 of supplementary gates in ZA110 resetting flip-flop D-B and D-C. When D-B and D-C are reset the reader and winder motors are turned off and the **bid request to the sequence control logic is removed.**

3.71 The negative input at pin B7 of ZA305 is a result of LA-1C, ZA321 sampling either an off-line condition or an end of sequence. If neither of these conditions exist, the input at pin B7 will be at 0 volt and the tape-out indication will be prevented from resetting flip-flops D-B and D-C. This logic prevents an incomplete start of message sequence to be transmitted when the tape lid is released during the sequence.

3.72 The power on, reset circuit at ZA401, is used to provide a collector set pulse to flip-flop D-B and D-C, a predetermined time after power is turned on. The action insures that the bid circuitry is not bidding for the line when the equipment is turned on.

Start of Message Delete Circuitry

3.73 The number delete circuitry provides the operator with the option of deleting the number sequence which normally precedes each message tape. Prior to operating the BID switch the operator determines if the message tape requires a number sequence. If not, the operator presses the NUMBER DELETE switch, providing a positive transition at the input pins A36 and B36 of flip-flop D-B on ZA112, if the on line signal applied at pin B14 of LA-1B, ZA114 is negative. If this on-line signal is at 0 volt, indicating the associated transmitter is on-line, the signal from the NUMBER DELETE switch is held at LA-1B ZA114 and does not switch D-B of ZA112 Refer to 7716WD, Sheet 3.

of LA-1B, ZA114 the indication from the NUMBER DELETE switch is presented to pine A36 and B36 of flip-flop D-B on ZA112. The D-B will be switched to the one state driving the output pin B34 negative. This -5 volts is applied to the input pin A4 of PA-2D on ZA108, driving the output pin A1 to 0 volt, which energiness relay K4 and lights the NUMBER DELETE lamp through K4 contacts. 3.75 The sumation relays at air B34 of flip flop D B is

3.74

With the -5 volts ca-line signal applied to pin B14

3.75 The negative voltage at pin B34 of flip-flop D-B is also applied as a prime at pin B26 of LA-1F, ZA103. The LA-1C, ZA103 is inhibited at this time due to the 0 volt supplied at pin B25 from pin B33 on D-B. When the BID switch is operated and D-B of ZA110 is switched as described in 3.62, a 0 to -5 volt transition is applied to pin A24 of LA-1C and pin A21 of LA-1F, ZA103. The output pin A27, of LA-1C, ZA103 is held at -5 volts due to the 0 volt present at input pin B25.

3.76 The output pin B28 of LA-1F, ZA103 is allowed to go to 0 volt due to -5 volts present at its other input pin, B26. The resulting positive transition at the output of LA-1F, ZA103 is used to set flip-flop D-C of ZA112 into the one state driving pin B26 to -5 volts. This level is inverted by LA-1D, ZA114 and applied to the sequence control logic as a number delete signal.

3.77 At the completion of a message the tape-out indication is received from the tape-out contact at the reader. This signal resets the bid circuitry as described in 3.70 and provides a -5 volt to 0 volt transition at pin B6 of PA-1C, on ZA106. This transition is applied to pin B32 of supplementary gate ZA112 providing a reset signal for flip-flop D-B. With the reset of D-B, ZA112 the NUMBER DELETE lamp is extinguished. On later acts, the reset signal for D-B of ZA112 is obtained at pin B6, A10 of PA-1C on ZA106. Refer to 7716WD, Sheet 2.

3.78 During normal operation (not in the delete mode) pin B33 of flip-flop D-B is at -5 volts. This is applied to the input pin B25 of LA-1C, ZA103 and permits a negative transition at pin A24 (3.75) to be inverted and passed to the flip-flop D-C as a reset signal. This provides -5 volts indication at the delete mode output, pin F7 of JA128.

3.79 A negative going transition, is received from the start of message (referred to as SOM - module B panel) sequence generator at pin E7 on JA128, upon completion of the SOM sequence. The signal is inverted by LA-2C, ZA305 and applied to pin B31 of supplementary gate ZA112 as a reset signal for flip-flop D-C. This reset signal is allowed to pass provided an on-line signal is present at the prime input pin A31, of supplementary D gate. When D-C is reset, the delete mode indication to the sequence control circuitry is changed to 0 volt. This permits the step pulses in the sequence control to be diverted from the SOM generator to the associated reader.

Figure 9- Block Diagram For Master High Speed Tape Sender

1-23 ISS 2, SECTION 592-851-130TC

| CLOC  | K         |            |

|-------|-----------|------------|

| RM TI | RAF       | ,≺o<br>-∕o |

| DUT   | (8)       | <b>⊷</b> ⊃ |

| AVA   | <u>IL</u> | ►0         |

Page 17/18

Step and Read Circuitry

3.80 During the reading operation, the operator has the option of stopping the reader and stepping it manually with the STEP READ switch. This circuit starts functioning when the STOP switch is operated and the associated STOP lamp is lighted. A level change from 0 to -5 volts is obtained at pin B4 of LA-2A, ZA103. Here again the output of a switch is fed through a dc (direct current) flip-flop configuration to remove contact bounce. Refer to 7716WD, Sheet 4.

3.81 When the reader is operating, the on-line signal input at pin B5 of LA-2A, ZA103 is -5 volts. As a result of the negative level being applied to pin B5 of LA-2A, ZA103 and the level change from 0 to -5 volts at pin B4, due to the STOP switch output, pin A9 is driven to 0 volt. This 0 volt is used as a reader stop signal and as a prime to flip-flop D-F of ZA110. The signal is used to inhibit the pulse to the SOM generator or the reader, thereby stopping operation.

3.82 The prime voltage applied at pin A2 of flip-flop D-F permits the positive transition, appearing at the set input, pin A1, to switch the flip-flop, driving the output pin, B3 to -5 volts. The positive transition at the input pin A1 is a result of operating the STEP READ switch. The output pin B3, of flip-flop D-F on ZA110, is inverted by LA-2E, ZA116 and supplied as a step read pulse. This pulse allows the reader to be stepped one character, and the character read by the reader to be transmitted on-line. To allow the reader to be stepped automatically by the incoming step pulse rate again, the operator presses the STOP switch returning it to the normal condition.

3.83 The resder may also be manually stepped off-line during periods when the reader is not normally being stepped by the incoming pulse rate. The STEP switch output is fed to a dc connected flip-flop configuration consisting of LA-1B, and LA-2B on ZA116. when the STEP switch is operated, a positive transition is obtained at the output pin A11, on the dc flip-flop. This transition is applied to LA-1B, ZA103, for inversion prior to being applied to the input pin B13, of LA-2B, ZA103.

3.84 If the second input pin, B12 of LA-2B is negative at this time, the input at pin B13 will be inverted and appear at the output pin, A11. The input level at pin B12 is 0 volt only when the STOP switch is in its normal position and at the time the on-line signal input is at pin B23 of LA-2C, ZA103 -5 volts. When this condition is met it is assumed the reader is normally being stepped by the incoming pulse rate, the manual step indications must be held.

3.85 The STEP switch is available for stepping the reader manually except when the reader is normally reading tape and stepped by the incoming step pulse rate received at pin D10 of JA128. 3.86 Assuming the input pin B12 of LA-2B, ZA103 is at -5 volts, the manual step indications at input pin B13 appear inverted at the output pin, A11. Then they are inverted twice by LA-2F, ZA103 and LA-1F, ZA116. At the output the manual step indications appear as positive transitions which are applied to the driver assembly..

3.87 The driver assembly is located in the tape transport

assembly and functions to change the low-level stepping pulses to a power level adequate for energizing the reader stepping coils. The stepping pulses delivered to the driver assembly come from **two** sources, one is the STEP switch described in **3.83**, and the other is the sequence control circuitry in the master logic. which are applied to pin D10, **JA128**.

**3.88** The LA-1A of ZA321 perform **the function** of preventing an alarm indication from occuring when the reader is restarted after **it** has been stopped and manually stepped by means of the STEP switch. This circuit IS required due to the characteristics of the verify logic.

3.89 The description of the following circuit is the same as described in 3.88. Input pin A7 of W-IA.

ZA321 samples the condition of the STOP switch. With the STOP switch in the stop condition, this input is -5 volts. Pin B7 of LA-1A, ZA321 samples the on-line signal, which is -5 volts and on at this point. The third input pin. A6 of LA-IA, ZA321 samples the STEP switch output at pin A17 of LA-1B, ZA103. When the STOP switch is operated again. pm A6 of LA-1A, ZA321 is at -5 volts. and the output pin A10 is driven to o volt. This positive transition is applied to the verifier logic where it is used to prevent an alarm on reader start-up when the contacts are again sampled.

#### Alarm Circuitry

3.90 There are two types of alarms provided in the reader logic. a VERIFIER alarm and a TAPE FEED alarm If either of these two errors occurs, an indication is received at pin A8 or B8 of JA128, setting an associated flip-flop D-D or DE of ZA110. There flip-flops are primed by the presence of an on-line indication. When either of the two flip-flops is set, an associated alarm lamp is lighted and a 0 volt indication is applied at either pin A1 or B1 of LA-2E, ZA103. The output pin B9 of LA-2E, ZA103 as inverted by LA-1E, ZA116 and supplied to the verifier as a 0 volt alarm signal. Refer to 7716WD. Sheet 5.

3.91 To reset the alarm flip-flops and extinguish the alarm indicator lamp or lamps. the operator presses the affected alarm switch. An on-line indicator lamp is lighted when the on-line signal is received. This indicator lamp informs the operator when a particular reader is allowed to transmit after a bid for the line has been entered.

#### B. Parallel to Serial Converter

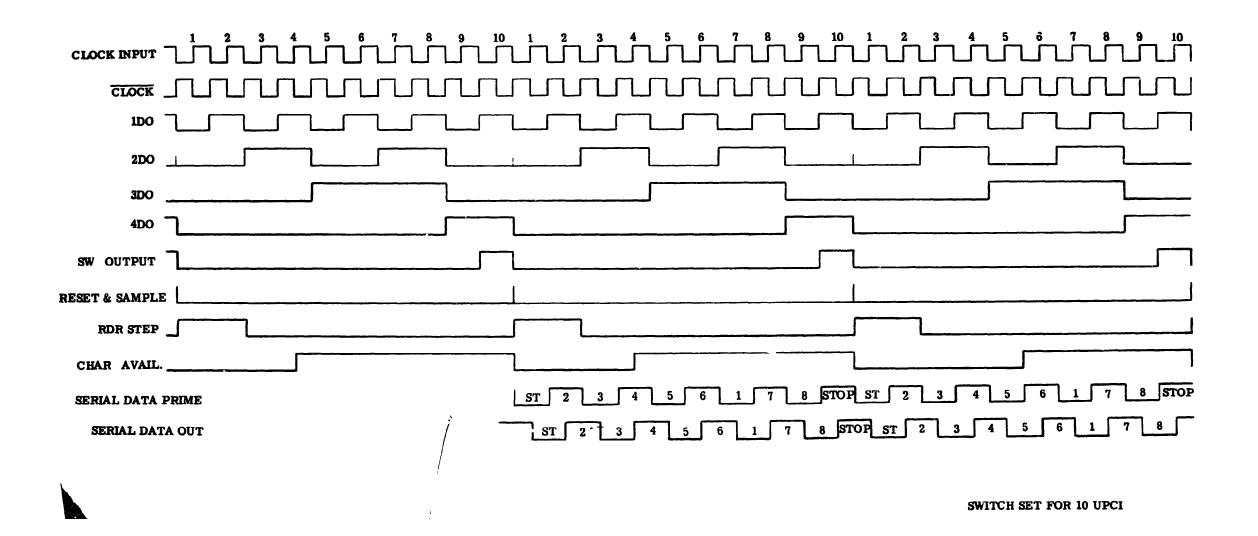

3.92 The primary functions of the parallel to arrial converter are as follows: (Refer to 7716WD, Sheets 8 and 9, and Figure 10 for block diagram).

- (a) Accepts an eight-level parallel signal, 0 volt for mark and -5 volts for a space, and converts this signal into a serialized signal output, +6 volts for mark, and -6 volts for space.

- (b) Accepts a clock pulse input at the bit rate which determines the speed of operation.

- (c) Provides a reader step pulse output at character rate.

- (d) Capability of working five through eight-level operation, start-stop or synchronous.

- (e) Optional parallel signal output is provided.

3.93 The parallel to serial converter, hereafter referred to as converter, includes a four stage binary counter which is capable of a maximum count of 16. It is also capable of being reset at a specific count by the UNITS PER CHARACTER INTERVAL switch, hereafter referred to as UPCI switch (module A), which will be explained later.

3.94 The counter is reset by a positive pulse coupled through diodes to the 1 side of flip-flops D-B, D-C, D-E, and D-F of ZA307. The positive pulse coupled to flip-flop D-B is first fed through the SIGNAL MODE switch (module A). When the SIGNAL MODE switch is in the START-STOP position, the 1 side of flip-flop D-B is reset to 0 volt by the reset pulse. When the SIGNAL MODE switch is in the SYNCHRONOUS position, the 0 side of flip-flop D-B is set to 0 volt by the reset pulse.

3.95 clock pulses, +6 volts to -6 volts, are fed to input circuit ZA302-A, pin B4. The input circuit converts the polar clock from 0 to -6 volts signal, 0 volt corresponding to a +6 volt input, while -6 volts corresponds to a -6 volt input. This neutral clock is inverted by LA-2D, ZA305 and fed to the input of the binary counter. The output of LA-2D on ZA305 also feeds LA-2B on ZA305. Since the clock has been inverted by LA-2D, ZA305 the counter counts at the negative going clock transitions. The outputs of all stages in the binary counter are fed to power amplifier which in turn feed the UPCI switch. Refer to 7716WD, Sheet 10.

3.96 NOR gates LA-1A, LA-1B, LA-1C, LA-1D, LA-1E, and LA-IF of ZA314 and LA-1B, LA-1D, and LA-1E of ZA305 and their associated OR gates ZA313-22, 21, 20, 19, 18, 17, 16, 15, and 14 detect the count in the counter. When the counter is reset in the start-stop mode, pins A32, B33 of LA-1D on ZA305, and pins A13 and B13 of OR gate ZA313-14 are at -6 volts. The output of 1A-1D, ZA305 is then dependent upon the other input pin B32. 3.97 LA-1D, ZA305 samples the contents of flip flop D-E of ZA319 when the counter is at the reset state. When there is a count of one in the counter, the output of LA-1E, ZA305 is dependent upon the input at pin B6 which samples flip-flop D-D of ZA319. Flip-flops D-F of ZA319, D-C, D-F, D-E, and D-D of ZA317; D-E, D-C, D-D, and D-E of ZA319 are sequentially sampled, each for the duration of the bit clock period. When the SIGNAL MODE switch is in the SYNCHRONOUS position, flip-flop D-E of ZA319 is not sampled.

3.98 The flip-flops mentioned in 3.97 stores information supplied from the verifier. If the one prime is at 0 volts, the flip-flop will store a mark when a complementary input is supplied a positive pulse. If the 0 prime is at 0 volt, the flip-flop will store a space. The primes for the storage flip-flops determine whether a mark or space is stored in a particular level. At the time a positive pulse is applied to the converter for reset, a character shift pulse is also applied to the complementary inputs of the storage flip-flops.

3.99 The output of the storage flip-flops are fed to program board ZA316 where the customer has the option of either sampling the 1 or 0 sides of the flip-flops. When the 1 side is sampled, a mark at the input will be sampled as a mark at the output. If the 0 side is sampled, a mark at the input will be sampled as a space.

3.100 The output of NOR gates LA-1A, LA-1B, LA-1C, LA-1D. LA-1E and LA-1F of ZA314, and LA-1B, and LA-1E of ZA-305 are fed to LA-1F, ZA305. The output of LA-1D, ZA305 is fed to NOR gate LA-1F, ZA305 only when the SIGNAL MODE switch is in the START-STOP position. The output of LA-1F, ZZA305 is the serial output. A 0 volt output of LA-1F, ZA305 represents a mark while a -6 volt level represents a space.

3.101 The counter can accept up to sixteen clock pulses before recycling. The number is dependent upon the position of the UPCI switch. If the switch is positioned so the counter counts above eight, each subsequent clock pulse will generate a mark or stop condition, until the counter is reset and again samples the storage flip-flops.

3.102 Levels eight, seven, and one from the verifier are fed through NOR gates 1-F, 1-D, and 2-D of ZA321, respectively. The outputs of these gates are fed to the converter Levels six five four three and two from the

the converter. Levels six, five, four, three and two from the verifier are fed directly to the converter. The character available signal from the verifier also feeds the converter.

3.103 The CODE LEVEL switch (module A), determines the number of code levels that are transmitted.When the switch is in the five-level position a 0 volt level is fed to NOR gate 1-F, 1-D, and 2-D of ZA321 which inhibits these gates. When the switch is in the six-level position, NOR

Page 20

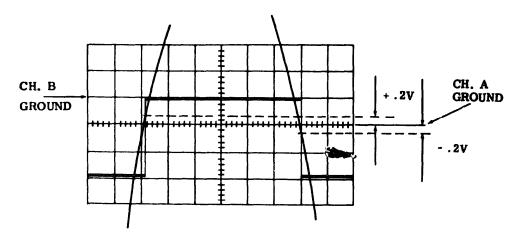

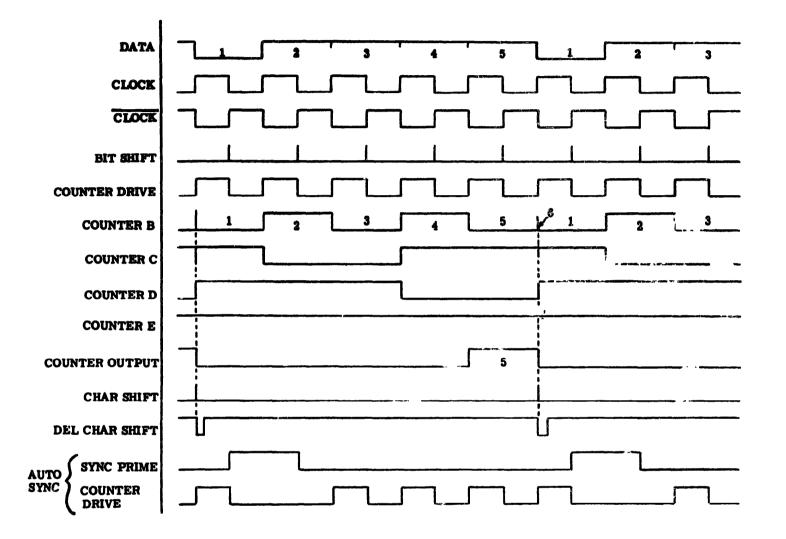

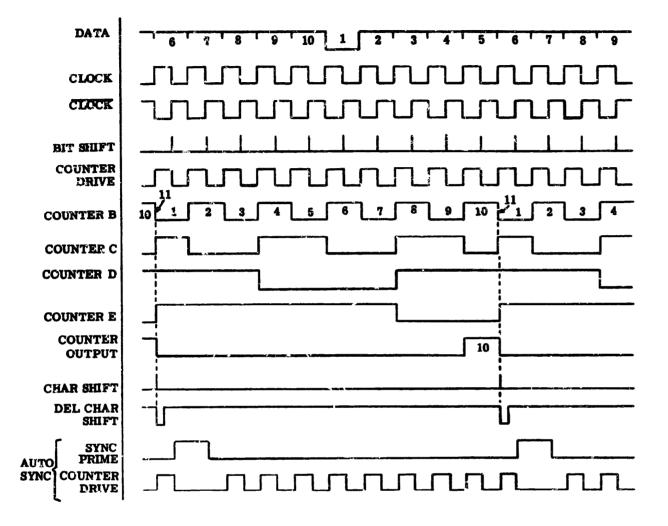

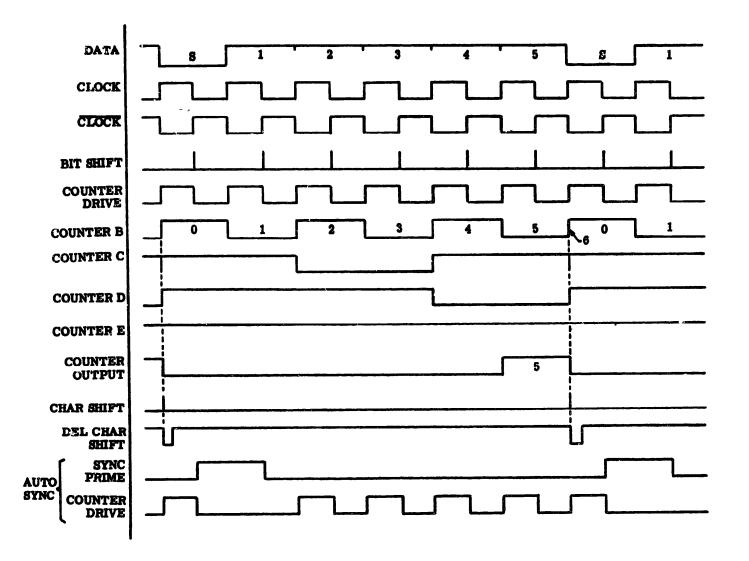

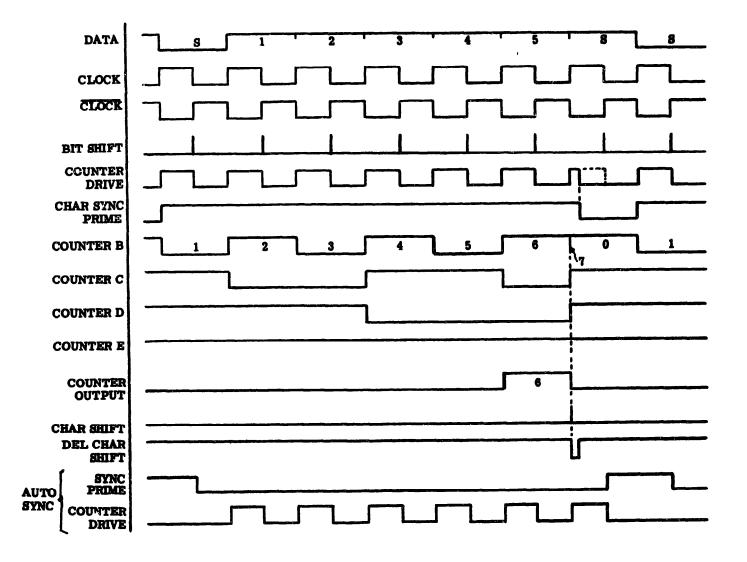

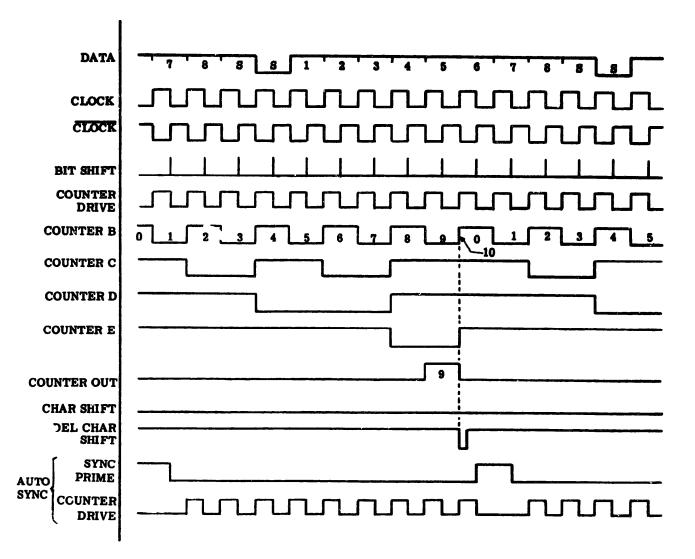

Figure 10- Timing Diagram for Parallel to Send Converter

1 - 2 7 ISS 2, SECTION 592-851-130TC

Page 21/22

gates 1-F and 1-D are held and so on through seven and eight levels. When a level is held in this manner, a mark is generated when the storage flip-flop which stores that particular level is sampled.

3.104 The parallel signal output from the venfier is also passed through output circuits ZA323-S, ZA324-B, ZA325-A, ZA325-B, ZA324-A, ZA325-C. ZA324-C, and ZA323-C. The output circuit converts its neutral input, 0 to -6 volts, to a polar output +6 to -6 volts respectively. The output circuits drive integrators, and time constants are determined by the customer. The outputs of the integrators are optional parallel signal outputs.

3.105 The character available signal from the verifier is also fed to the set input two millisecond delay ZA311-A whose prime is permanently grounded. The normal output is fed to output circuit ZA326-A, and the auxilisry character available output is a two millisecond wide positive pulse.

3.106 The UPCI switch is a four section switch which samples the outputs of the binary counter. The four poles of this switch are fed to NOR gate 1A of ZA303.

Pin A8 of this gate is fed from OR gates ZA313-13 and 12 which sample the send number lead from the SOM generator. The send number is strapped to either JA128-G4, H4, G3, or H3. During the SOM sequence, the send number lead is a 0 volt which inhibits LA-1A of ZA303, and disables the UPCI switch.

3.107 The output of LA-1A, ZA303 primes pin B4 of LA-2A, ZA303 for its other input pin B5. The latter gate thus samples the combined outputs of NOR gates 1-F, 1-D, 1-B and 1-C, of ZA303. Depending upon where the send number lead is strapped, one of the above named NOR gates will be primed while the others will be inhibited during the SOM sequence. The other inputs of these gates sample the outputs of the binary counter.

3.108 If the send number lead were strapped to JA-128-H3, a count of nine in the counter will place a -6 volts at all the inputs of LA-1C, ZA303 which drives the output to 0 volt. This 0 volt level is fed to already primed LA-2A on ZA303 which inverts the signal and feeds -6 volts to the converter. This -6 volt level is then inverted again by NOR gate LA-2A and LA-2C of ZA314 and appears as a 0 volt level for a count of nine in the counter.

3.109 The outputs of NOR gates LA-2A and LA-2C of ZA314 are fed to PA-F and PA-E of ZA311. When the next clock pulse steps the counter, the output of LA-1C of ZA303 drops to -6 volts. Consequently a negative transition appears at the input of PA-F, and PA-E of ZA311. The positive pulse resulting from the negative transition resets the counter to either 0000 or 0001 depending upon mode of operation. 3.110 The positive pulse at the output of PA-E, ZA311 is fed to the complementary inputs of the storage

flip-flops. It is at this time that the information from the verifier is fed into storage and becomes the next character to be transmitted. The positive pulse is also fed to the set one input of flip-flop D-B of ZA317. Refer to 7716WD, Sheet 10.

3.111 At the end of the SOM sequence, the send number lead goes to -6 volts and holds LA-1C of ZA303

placing a -6 volt level at pin A8 of ZA303. NOR gate LA-1A, of ZA303 now samples the UPCI switch. Depending on the position of this switch the counter is either reset on the sixth through sixteenth clock pulse (START-STOP) or fifth through sixteenth (SYNCHRONOUS).

3.112 Flip-flop D-B, ZA317 is reset when the counter steps to a count of two. The normal output of flipflop D-B is fed to LA-2E of ZA303. At the output of this gate there are negative pulses whose duration is either one or two clock pulses, depending upon the mode of operation. The interval between leading edges is determined by the UPCI switch or send number strap connections (during the SOM sequence). This is the character interval. The output of NOR gate LA-2E of ZA303, the reader step lead, is fed to the verifier where it is used to generate various timing sequences.

3.113 The serial data output from LA-1F of ZA305 primes flip-flop D-D of ZA307. LA-1E of ZA303 inverts the serial data input applied to the prime 0 of the flip-flop in such a way that if the 0 side is primed, the one side prime is at -6 volts or the sequence may be reversed. The bit sample from the converter (which is at clock pulse time) is fed to the complementary input of flip-flop D-D, ZA307.

3.114 Previously it was stated that the counter was stepped by the inverted clock, with the bit sample at clock pulse time. Thus, flip-flop D-D is primed a half of a bit time before bit sample occurs. The output of flip-flop D-D is fed to output circuit ZA323-B where a +6 volt output represents a mark while -6 volt output represents a space.

3.115 A polar (+6 volts) abnormal traffic indication signal on input connector JA128 pin C4 is fed by external equipment to input circuit card ZA302-B. The output of this input card is fed to PA-1C of.ZB1315, input pin A9. The output load of this power amplifier is from the coil of relay KB501-B.

3.116 With the abnormal traffic input positive, relay KB501-B is de-energized and the associated contacts are open. Driving the abnormal traffic input negative energizes relay KB501-B. The relay contacts close providing a ground return for the abnormal traffic indicator lamp on the master and supplementary reader cabinets.

#### C. Sequence Control

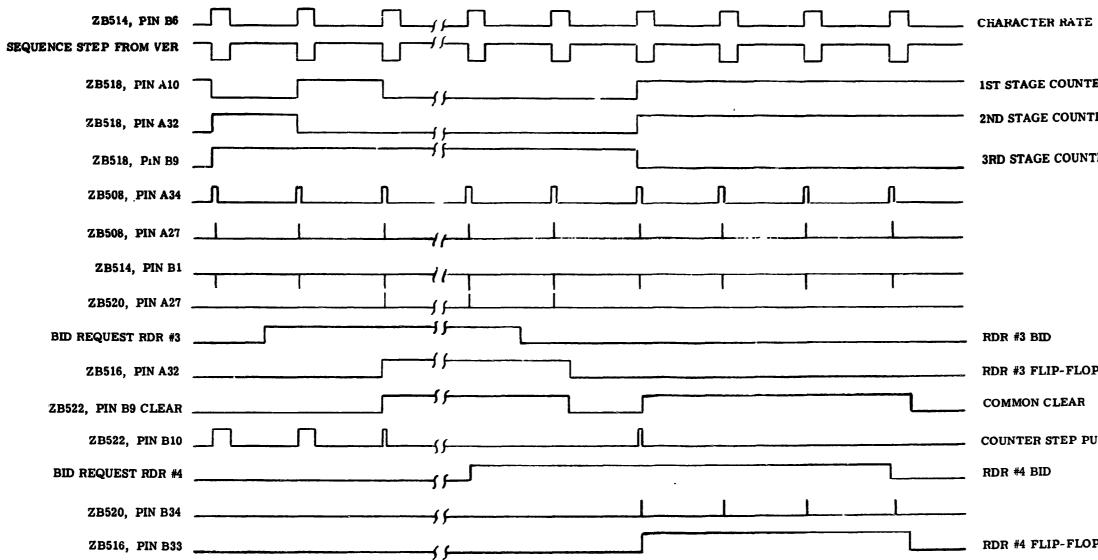

3.117 The sequence control logic assures that only one reader out of the six is capable of supplying signals to the verifier at any one time. (Refer to 7716WD, Sheets 13 and 14.) The circuitry shown on Sheet 13 provides for bid requect inputs from up to six readers. Since the logic for each reader is identical, the sequence of operation will be described for reader number three only.

3.118 When a bid request (0 volt) is received at pin G2 of JB128 it is inverted twice by LA-2C, ZB520 and LA-2F, ZB505. An inverted signal is taken from pin A26 of ZB520 to be applied to pin B25 of the flip-flop ZB516, D-C as a reset prime. The bid request input therefore primes the flip-flop at pin A24 in preparation for a set oue input at pin B24. This pin receives a zero transition from the output of LA-1C, ZB520 at a time when all inputs of this gate go to a -5 volt level. Three of the inputs to this gate sample the output collectors of a three stage counter composed of flip-flops D-F, D-C and D-E, ZB518.

3.119 The one side of the first stage is sampled at pin B24, the one side of the second stage is sampled at pin B25, and the zero side of the third stage is sampled at pin A24. The fourth gate input is a character clock signal. The third step pulse input to the counter, along with the character clock input at pin A32 of LA-1C ZB520, results in an output at pin A27 of ZA520 as shown in Figure 11. The bid signal input primes pin A24 of flip-flop DC, ZB516 at this time, as shown on Figure 11. The output of ZB520, pin A27 when applied to pin B24 of flip-flop DC, causes it to go to the set condition (Figure 11).

3.120 The resulting 0 volt at pin A32 of flip-flop D-C is also applied to NOR gate LA-1E, ZB522 where it is used as au inhibit signal for subsequent step pulses arriving at pin A2 of this gate. (Figure 11, shows these step pulses being inhibited.) The inverted output of flip-flop d-D, pin B26, which was driven to -5 volts when the flip-flop was set, drives PA-1C, ZB508 into saturation.